Other Parts Discussed in Thread: LM706A0, LMQ61460, LM70880-Q1

Tool/software:

Hello Ti forum,

I would like to know what the reference plane is for the Switch Node when using the LM706A0-Q1 in IBB configuration.

1. Is the Switch Node referenced to the GND of the IC, which in the IBB case is -Vout.

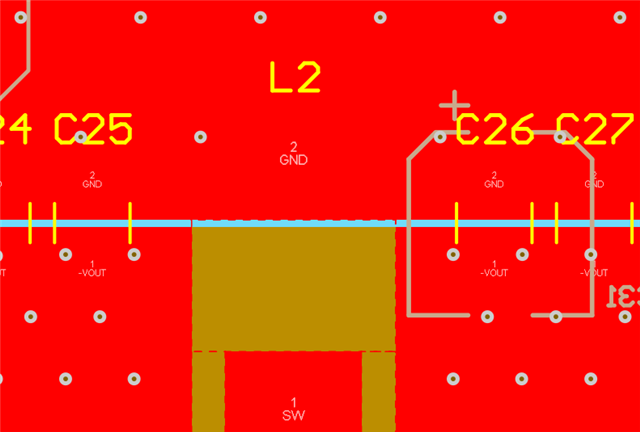

I am investigating the better layout when using a shielded inductor.

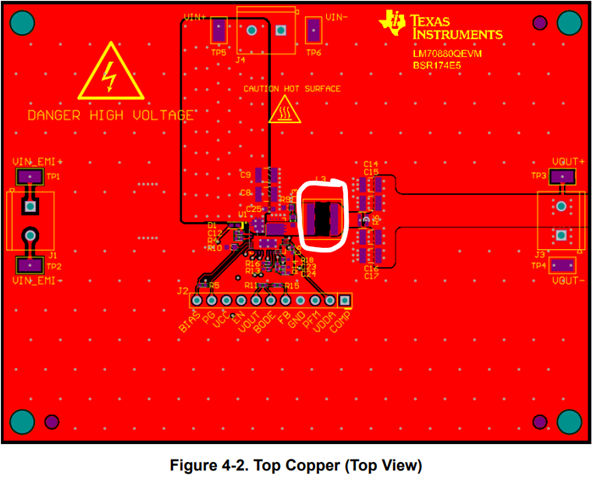

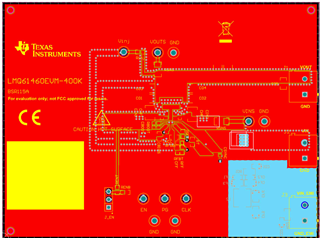

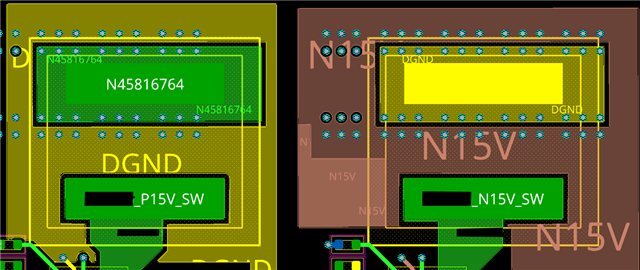

Application notes and design reviews, including LMQ61460 EVM, indicate to use the GND referenced copper pour directly under inductor, as well as a solid plane layer 2 for example also referenced to GND.

Now with the IBB case the IC GND reference is -Vout.

If the Switch Node is referenced to GND IC, should one apply the copper pour to -Vout?

It is understood that the current loops are different in the IBB case.

I am planning to apply the same copper pour directly under the inductor as well as a solid plane on the next layer down, same as in standard configuration.

This copper pour is referenced to -Vout, IBB Case, instead of GND in the normal case. An example of GND under Inductor is attached.

Please let me know your thoughts on this issue.

Thanks,

David