Other Parts Discussed in Thread: UCD3138

Tool/software:

Hello:

The application issues for customer UCD3138A are as follows:

The application is a constant current source project, and during debugging, it was found that there was a sudden change in the DPWM cycle. The following experiments were conducted to address this phenomenon:

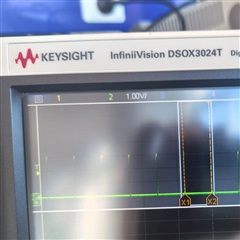

The program runs in an open loop, and in the first experiment, it was verified using the demo board of TI. It was found that this cycle is stable, but does not match the calculated value. The cycle set to 16000 should correspond to a cycle of 4us, but the measured value is 4.045us, which is 45ns larger than the calculated value,

The second experiment, also an open-loop operation, was tested on the customer's own board, and a sudden cycle change occurred again. The phenomenon is that every 3 to 4 cycles larger than the theoretical value, a cycle of two durations of 4us suddenly appears;

The customer's question is, is it reasonable for the actual cycle to differ too much from the theoretical value? How to avoid the phenomenon of the second cycle jump?

This has always been a problem in previous applications, but most of the previous projects were constant voltage source projects, which did not require high output voltage ripple and did not affect usage, so we did not pay attention to this situation. The recent constant current source project has very high requirements for output current ripple, and even the smaller the current ripple, the better. When the customer measured the ripple, they found that there was an irregular jitter in the current ripple under open-loop conditions. Therefore, it was traced that the period given by UCD3138A was fluctuating.

The first picture below shows a strict cycle of 4us, and the duration of the next cycle increases by about 20ns

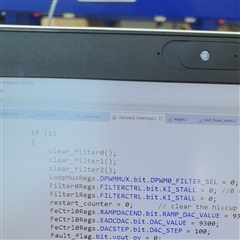

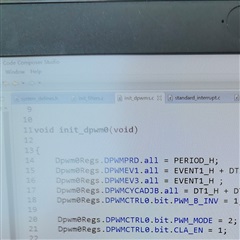

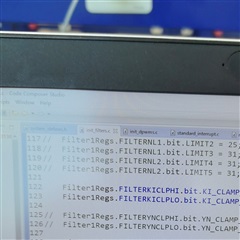

The power stage is not working, only UCD3138A is operating in open-loop mode, which has little to do with the peripheral circuit. The customer thinks there may be a problem with the software settings and wants to seek help from TI's technical support to investigate this situation.