Tool/software:

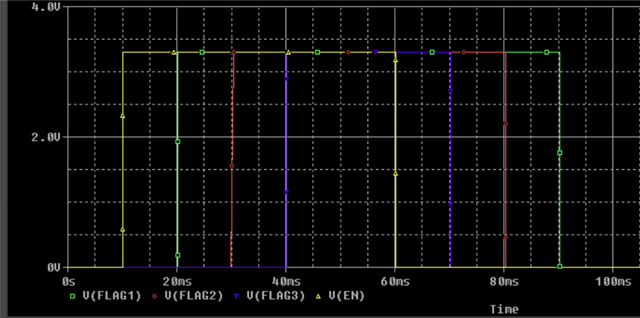

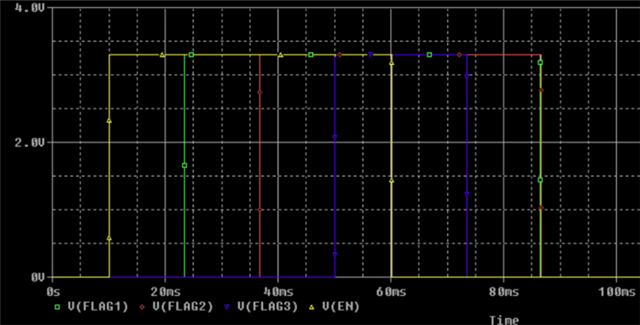

I have two circuits that are pretty much identical in pspice, and I'm getting very different results. For example, in the second circuit, Flag2 and Flag1 deassert nearly simultaneously. Here are the netlists:

Circuit 1:

* source FPGA SEQUENCER

X_U2 EN VCC3V3 FLAG1 FLAG2 FLAG3 0 LM3880_TRANS PARAMS: SEQ_DESIG=1

+ TIME_DESIG=10m

R_R9 FLAG1 VCC3V3 10k TC=0,0

R_R10 FLAG2 VCC3V3 10k TC=0,0

R_R11 FLAG3 VCC3V3 10k TC=0,0

V_V9 EN 0

+PULSE 0 3.3 10m 100u 100u 50m 150m

V_V10 VCC3V3 0 3.3

Circuit 2:

* source TEMP

X_U1 EN VCC3V3 FLAG1 FLAG2 FLAG3 0 LM3880_TRANS PARAMS: SEQ_DESIG=1

+ TIME_DESIG=10m

V_V1 VCC3V3 0 3.3

V_V2 EN 0

+PULSE 0 3.3 10m 100u 100u 50m 150m

R_R1 FLAG1 VCC3V3 10k TC=0,0

R_R2 FLAG2 VCC3V3 10k TC=0,0

R_R3 FLAG3 VCC3V3 10k TC=0,0

It seems I'm unable to get the LM3880 spice model to accurately simulate. Any suggestions?