Other Parts Discussed in Thread: TPS65224, AM62A7

Tool/software:

Hello, engineers

When we used GPIO5 of the TPS65224 to perform ADC acquisition, we found that the ADC acquisition port of the chip would automatically enable a pull-down resistor by default. This caused the ADC voltage division value to decrease in a stepped manner when we were collecting the voltage. Moreover, the higher the collected voltage, the greater the voltage drop. We attempted to modify the bit 3 of the GPIO5 register to disable the pull-up resistor, but it had no effect. Only when setting GPIO5 bits 6 and 5 to GPIO mode did it work.

Could you please tell me if there is any other way to close this dropdown menu?

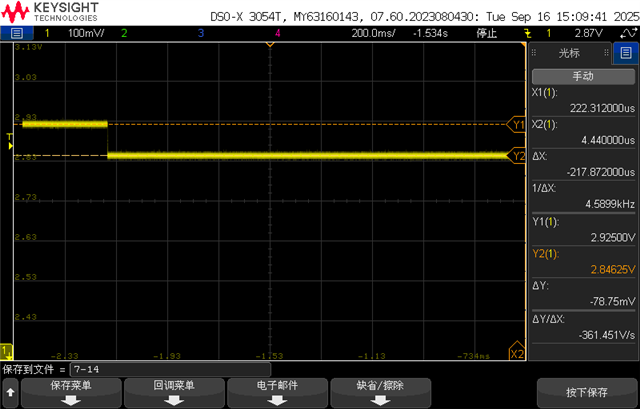

The figure below shows the change in the AD voltage divider value after I enabled the ADC acquisition.

At this moment, my collected voltage is 32.5V, and the voltage is divided by 100K and 10K resistors.

Thanks,

xiwen