I am using the TPS63700 to generate -5 V, but the output is not designed to discharge the converter output when the converter is disabled. This function is added with an external RC circuit that enables a P-channel transistor to discharge the -5 V converter output to 0 V in order to get proper sequencing relative to other power rails. However, in some case this scheme partially fails, and part of the problem seems to be that the timing for disabling is not described in the datasheet.

In the external circuit a capacitor (1 µF) is connected between EN and gate, while a resistor (10 kohm) is connected between gate and ground. The drain of the P-channel transistor (DMG1013UWQ) is connected to the -5 V supply, and the source to ground.

The rising edge of EN will enable the converter, while the capacitor will slowly charge (time constant 10 ms) to the voltage of the EN signal relative to ground. Much later the falling edge of EN is supposed to disable the converter and pull down the gate of the transistor (via the capacitor) thus letting it conduct and discharge the -5 V supply to ground until the capacitor is discharged to ground.

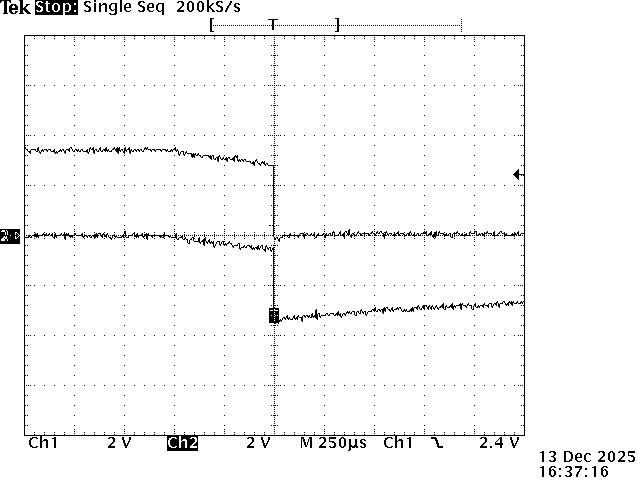

One board works just fine, but another partially fails as the output voltage immediately is pulled from -5 V to 0 V, but then after 16.5 ms the output unfortunately partially reverts to -920 mV. If the resistor is changed to 100 kohms, the problem disappears. I suspect that the converter in some cases is a little slow to turn off. Any thoughts?

I failed twice submit the above with the Edge browser but am trying Firefox now.

eft): VCAT (nominal -5 V)

eft): VCAT (nominal -5 V)