Hi,

I have an application where I use the LM22670 as voltage inverter LM22670 Evaluation Board Inverting Topology and Application Notes (Rev. D).

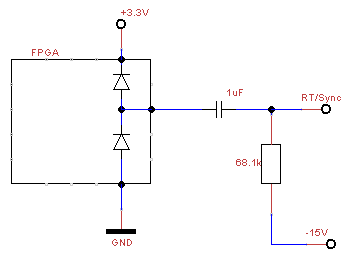

Now I want to synchronize it through the SYNC pin. The above AN tells me something of using a level shifter to get a GND referenced sync signal. But this is a little more comlicated than simply using a capacitor in series. With other simple switchers I already used this decoupling capacitor in series to the SYNC pin and this worked fine (at least for the LM2670 as voltage inverter (of course with a resistor to the ground pin) .

Question: is it possible to decouple the sync signal for the LM2267x also by using a capacitor? If yes, what pulldown resistor is recommended?

Many thanks in advance!

Wolfram