I'm working on a 10 KW 2-phase BCM buck converter based on the UCC2806x but got stuck. I've 'folded' the math and ins/outs so it works for buck application, and the circuit is working quite happily for a range of in- and outputvoltages. For any other range, strange things happen. This range is not clearly defined, but lies in the range of Vin=2xVout. Above and below is no problem (30KHz switching freq. works just as nice as 120KHz)

What happens is that immediatly after the gate driver (IRS21850 single high side) is turned off and current starts falling, the controller turns the gate on again, thus ramping current further up until it hits the current limit of the lab supply used. Most of the time the gate drivers don't survive. The same thing happens when GDB is disabled, when VINAC, VSENSE and HVSEN are externally controlled and when seperating or not seperating PGND and AGND.

I've looked at it with a few colleagues, redesigned grounding and signal routing and ruled "everything" external out. The feedback may not look stable, but this is pickup. Gate B is completely disabled and remains so, even when A decides to turn on. When connecting gate B to Comp, the controller works fine until A starts misbehaving and then chaos happens, as can be expected. So, for tests, i've disabled B.

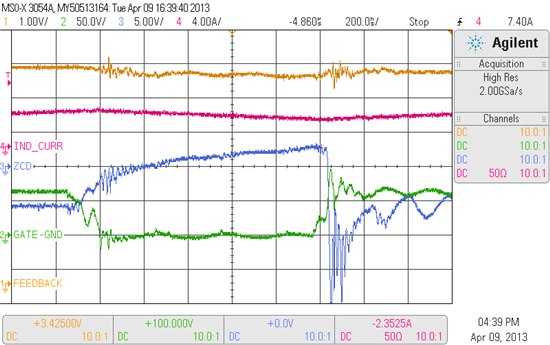

Green = Gate of MOSFET A vs GND (so a bit dirty, sorry for that, we've not kept every screenshot)

Blue = ZCD winding of A vs GND before RZCD

Purple = IL,A

Then we have (different scope, different day)

Top: VGS (diff probe) MOSFET

Bottom : output of Controller GDA

Clearly, the controller is first to turn on again. Not the FET, not the Driver, not the Current Sense winding, but the Controller itself. I've got more scope shots of all the other signals to reaffirm this statement.

I could list everything i've done, but in the beginning there was almost no decoupling and/or limiting switching speed and long wires. Now everything is limited, filtered and built on the controller itself. I've used other power supplies, coax or twisted wire. I've also eliminated reflections and ground bounce from controller to gate driver. All signals, supplies and ground became cleaner and cleaner, but no difference in behaviour.

Why does the controller decide to switch on again, with no apparent external cause?