I want to evaluate NexFET for synchronous rectification, but the provided SPICE models don't work in Orcad Capture 16.3.

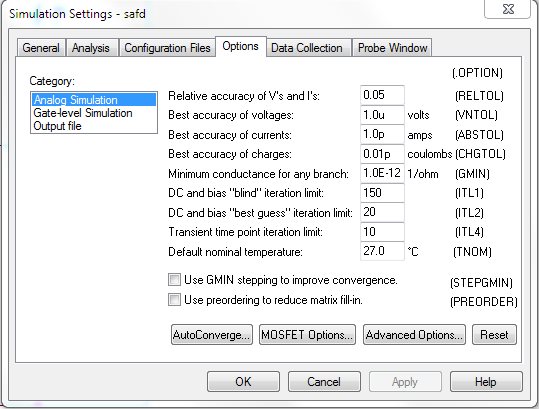

Initially, I put the NexFET SPICE model in a circuit that was initially working with a MOSFET model from IRF. When it didn't converge with the NexFET, i tried all the usual trouble shooting techniques (adding parasitics, lowering minimum timestep etc.).

After much work, I narrowed the error down to this:

1) MOSFET is fully on (Vgs >> Vth), with current going from source to drain (ie. synchronous rectification)

2) MOSFET is turned off (Vgs < Vth), current should commutate from channel to body diode (ie. dead time)

At 2), the simulation will fail to converge.

I have tried with the SPICE models of the following NexFET devices, all fail to commutate from channel to body diode:

CSD18503KCS

CSD18532Q5B

CSD18534Q5A

CSD18532KCS

Please find attached an Orcad Capture 16.3 project that you can use to replicate the error.

Best regards,

Kristian Lindberg-Poulsen

3718.NexFET_SPICE_bodydiode_bug.zip

PS: Why the hell do you have to encrypt the SPICE model? It's a frickin' MOSFET... The usability of the model is heavily reduced - for example, I can't set the model gate resistance to zero and add an external resistor so I can see the actual Vgs behind the internal gate resistance... Hell, I would probably be able to fix the body diode problem myself if it wasn't encrypted... PLEASE reconsider this encryption policy.