We have a design that using a TPS63000 - Buck-Boost Converter providing power to the TPS79928 LDO.

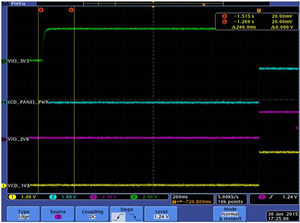

We are seeing an unexplained pulse out (VIO_2V8) of the TPS79928 LDO when the enable signal (seen below as LCD_PANEL_PWR) is low the whole time from power-on-reset.

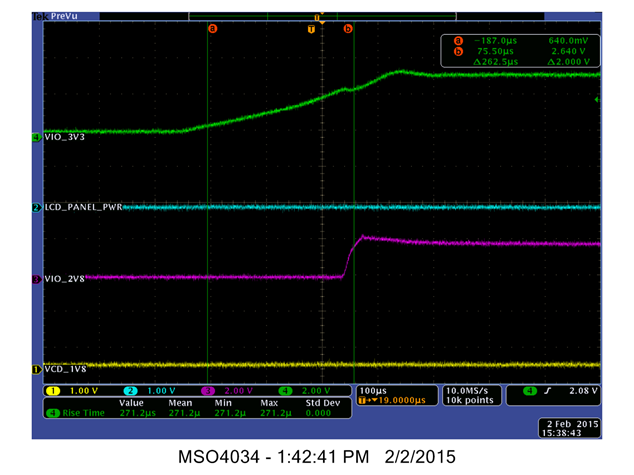

Currently this issues seem related to the rise time for the TPS7992 input but we don’t see any rise time requirements in the TPS79928 specifications.

We have connected the TPS63000 in our system to the TPS799xxEVM-105 and see the same noise in Figure 1 below.

Figure 1 below shows the unexplained pulse and figure 2 shows the pulse gone after adding a soft start circuit to TPS63000 thus slowing down the rise time to the TPS79928 input.

TPS79928 (IN) - VIO_3V3 (GREEN)

TPS79928 (EN) - LCD_PANEL_PWR (BLUE)

TPS79928 (OUT) - VIO_2V8 (PINK)

Figure 1: Pulse on output seen with Enable (LCD_PANEL_PWR) Low.

Figure 2: Soft start circuit added to TPS63000 to slow down the rise time to the TPS79928 Input