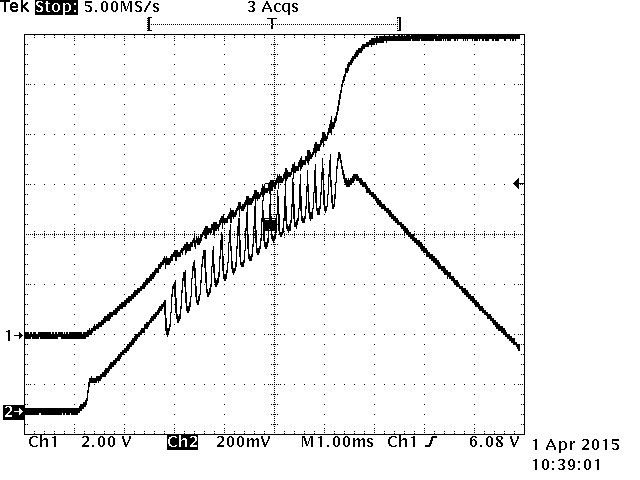

Based on very recent TI recommendations, we've eliminated the dV/dt MOSFET gate drive approach originally being used. Not surprisingly, an oscillation is observed on inrush ramp-up, arising when the Vin DC supply enters CC mode at 2Amps with the inrush limit set to 10Amps. When the supply is driven into CC mode as the MOSFET current slews up, Vin momentarily drops below the EN pin threshold, rapidly shutting the MOSFET down. EN serves as the UV monitor for Vin through a divider network per the TI example application. When Vin recovers and again crosses the EN threshold, the MOSFET current slews up rapidly, repeating the cycle. The intentionally thin decoupling on Vin permits a short cycle time, observed to be around 6.2kHz. This clearly demonstrates that the inrush current needs to be carefully chosen with respect to the capabilities of the source, and for hot insertion applications, the design needs to ensure the controller is enabled only after insertion is mechanically settled, requiring more than a simple divider network on EN.

What was unexpected, however, was that the TIMER pin exhibited similar oscillation on its rising slope, displaying rise/fall edge rates that defy explanation by the functional block in the datasheet (Figure 5). When the MOSFET shut down by EN, the TIMER cap discharged by about 200mV with a current far greater than 10uA. When the MOSFET turned back on, the TIMER cap voltage also rapidly recovered the 200mV drop, somewhat slower than it fell but still far faster than expected from a 10uA charge current. During this oscillation event, which lasted through much of the Vout risetime of around 6-8msec, the overall slope of the TIMER pin voltage remained monotonic but shallower than the normal linear ramp, roughly doubling the timeout limit.

During the investigation, the EN pin network was changed from a resistive divider from Vin to a long time-constant R-C filter without voltage division. The oscillation disappeared, both on Vout as well as on the TIMER pin, with the Ct charge-discharge cycle exhibiting linear ramps as expected by the 10uA sources. It is apparent the the EN pin has an effect on the TIMER pin that is not fully explained in the datasheet. We are are looking for two answers from this post;

First, explain how the TIMER Ct voltage can exhibit 6.2kHz 200mV pk-pk oscillation on a 47nF capacitor, from a pair of 10uA current sources.

Second, are there any simple example designs that take EN out of the Vin loop during inrush but still utilize it as a UV monitor function? A larger hysteresis on the EN input comparator would increase its immunity to Vin transients, but there is no way of adjusting it. R-C filtering seems to be the simplest option, but may prove troublesome on momentary losses of Vin.