Hello:

I'm hoping someone can explain the specific conditions that cause the over-current circuit in the TPS40210 to shut down the supply. The datasheet say if the ISNS pin sees a voltage over 150mV the supply will shut down. However, it doesn't say if one pulse will cause it to shut down or if the condition has to persist for a certain amount of time (or pulses).

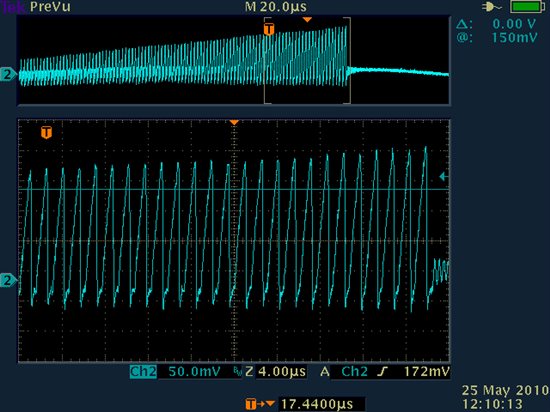

My current design is feading a load that takes periodic transient currents. During these transients I see the voltage on the ISNS pin start to rise, but the supply doesn't shut down until the pulses are around 230mV.

My question is this, why are the pulses reaching 230mV? Is the chip out of tolerance, or is it because the current is getting that high during a time out period. If there is a time out period, what is it based on, and can I change it?