project details

input 60-201V line to line three phase at 30-106Hz

Expected bulk DC voltage is 78-261Vdc

output 24Vdc at 2A

Primary side regulated off-line converter

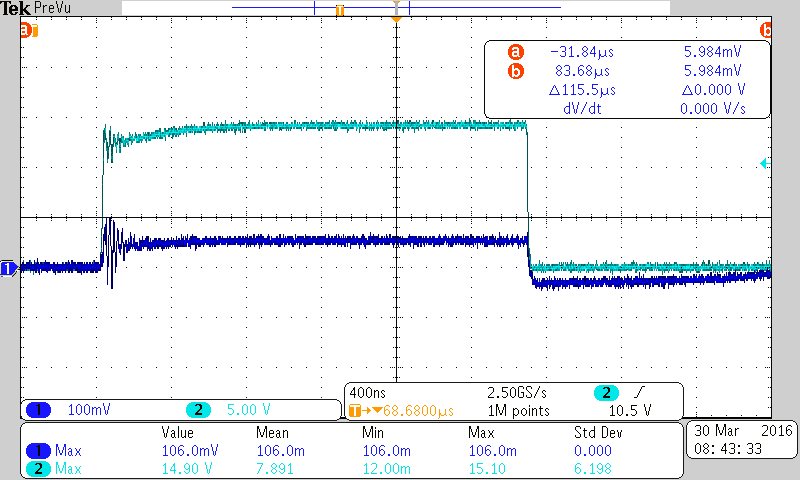

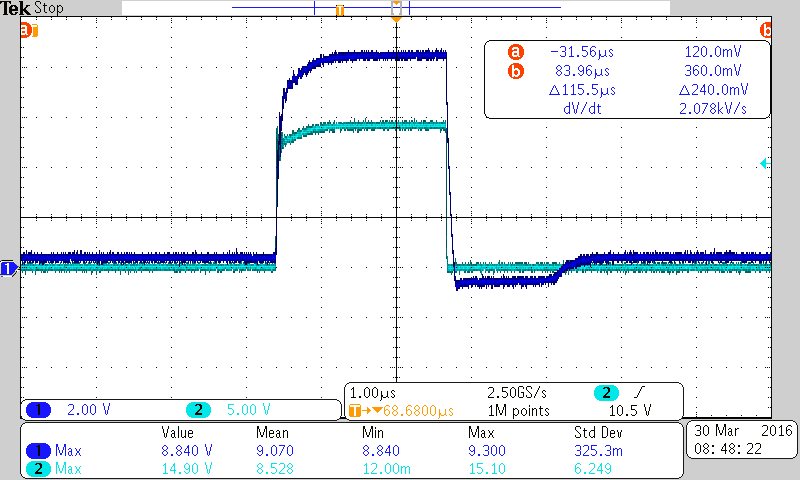

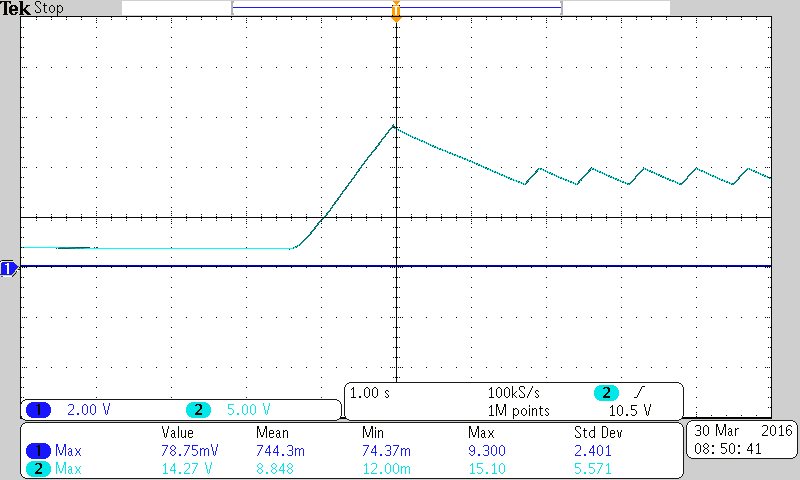

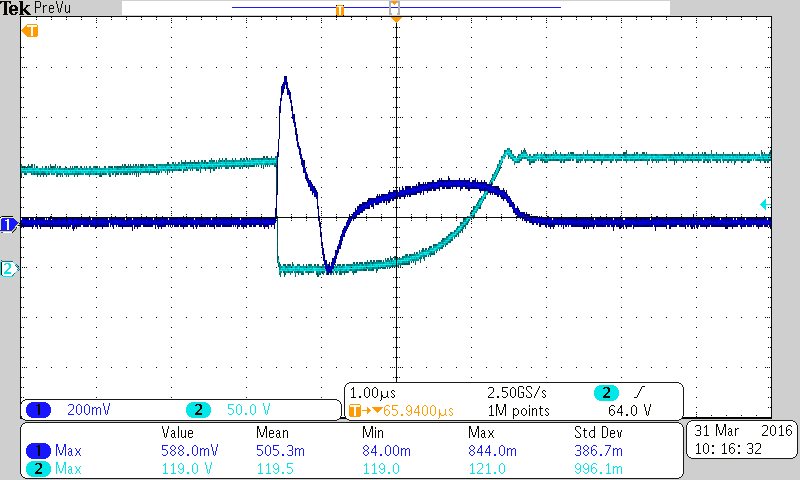

I made a schematic from PMP9643 and the Excel design calculator, which is below. The circuit board was layed out and prototype made. The prototype has been checked for connection errors. When connected to 100Vdc the VDD charges to 15v, then discharges to 11v, then plummets to 4v and starts all over again. see attached image for oscilloscope picture. The gate driver doesn't fire and seems to be disabled. Also the SD pin holds low despite the 19.1K oh resistance to ground at room temperature.

Why wont this chip fire the drive pin? Is the chip suitable for the input?