Hi,

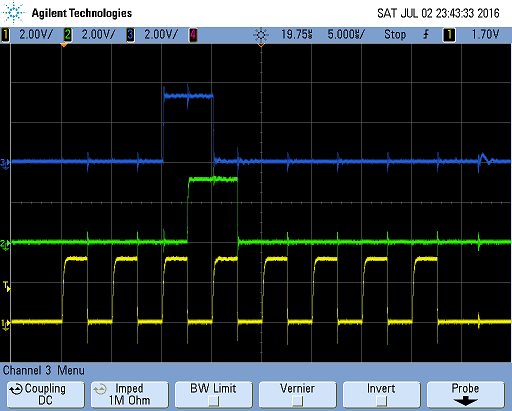

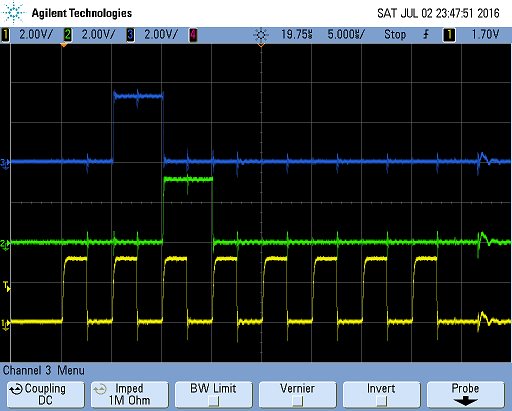

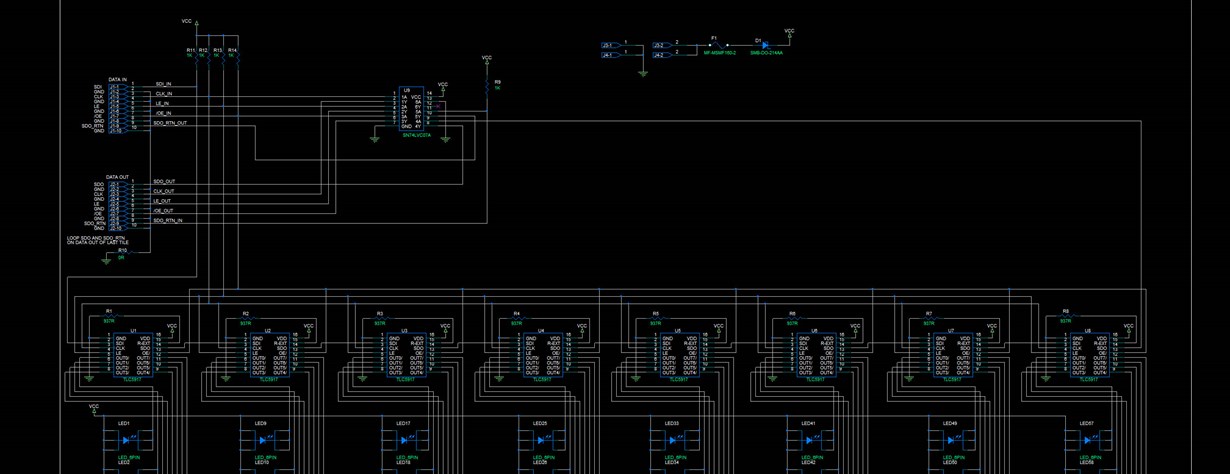

We are designing a digital display sign and are prototyping using TLC5917s, we have used these before on other projects without a problem though they have all be in one cascaded screed. In this job we have 8 TLC5917s cascaded on each board and are trying top cascade multiple boards but the clock and data seem to be out of sink. We looked at this on our scope and we have the the rising edge of the clock bang in the middle of the data bits on the input to the first chip, however on the SDO data out from the first chip the relationship between the clock and data has shifted by almost half a clock cycle (on the first chip) and now the data bit is just getting sampled by the clock. This is replicated over the next seven TLC5917, they all work but it just looks wrong having the rising edge of the clock right on the edge of the data pulse. When we try and drive the second board through a buffer IC the tiny delay caused by the buffer is enough for the next board to miss the correct slot and clock the data into the next bit in the register. We have slowed down the SPI to 200K but this makes no difference. We were planning on using several hundred of these per sign, but seem to have hit a brick wall for the moment. Any advise appreciated.