Hello,

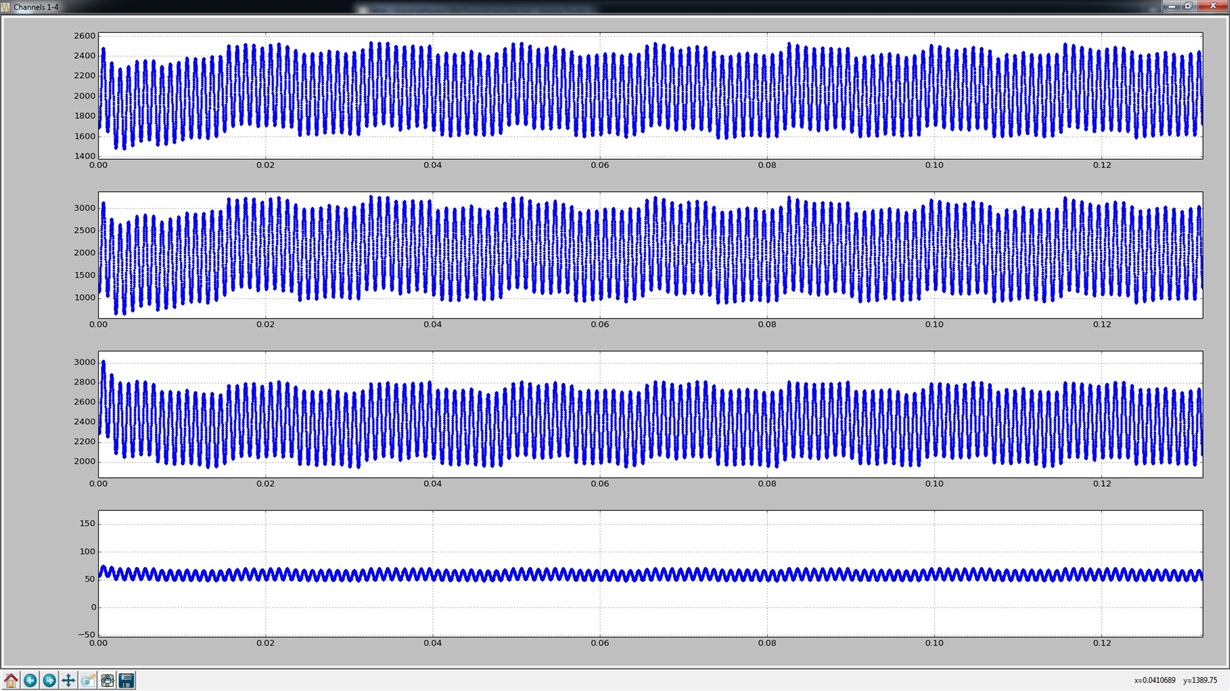

I've recently changed my buck switching regulator to an LM43600. The issue I'm having is that it doesn't seem to increase the duty cycle under load. I'm kicking of a Tiva Arm and ADC and this transient is dragging down my 3.3V rail by 20mV. This is causing a voltage drop in the VCC of the analog filters that are also powered by 3.3V. I can see it in my data and with amplification is very bad. It goes back up 20mV and returns to normal when I'm done sampling etc...it just tracks the burst of sampling and the processor.

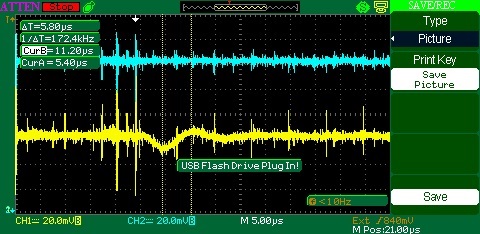

Here is a pic of my voltage rail drop:

Here is a screen shot of the output voltage tracking the feedback pin on the eval board. It just sits down for an extended period of time. Blue rail is Vcc (output of the LM43600...same as above. Bottom/Yellow trace is the feedback pin of the regulator. The probe was placed on the eval board between resistors Rfbb and Rfbt)

When I look at the duty cycle of the switch it looks like it just sits around 50%, in fact 50% exactly. I'm using the LM43600 evaluation module from TI and i haven't modified it so it is running at 500kHz. The data sheet said the part has a Toff min of 250nS. I would think this part would try to correct for this drop. I lose 20mV on Vcc for the amount of time I'm sampling. Basically, it looks like if I attach a load I get this long voltage drop. I've tested it up to 300mS which is more than enough time to recover.

I'm powering the LM43600 evaluation card with a bench top supply set to 8V at 0.5A.

Here is the link that shows the card and the schematics.

I'm not an analog/PS designer but usually the pulse width just increases to maintain a steady voltage even if there is a transient like this.