Hi....

One of my customer is using TPS62561DDCR for 3.3V / 600mA output design. They have already consumed 30K devices but recently they received the cards from field & observate that in 4 to 5 boards TPS62561 device were damaged.

Switching node is showing short circuit with ground, i.e lower MOSFET seems damaged.

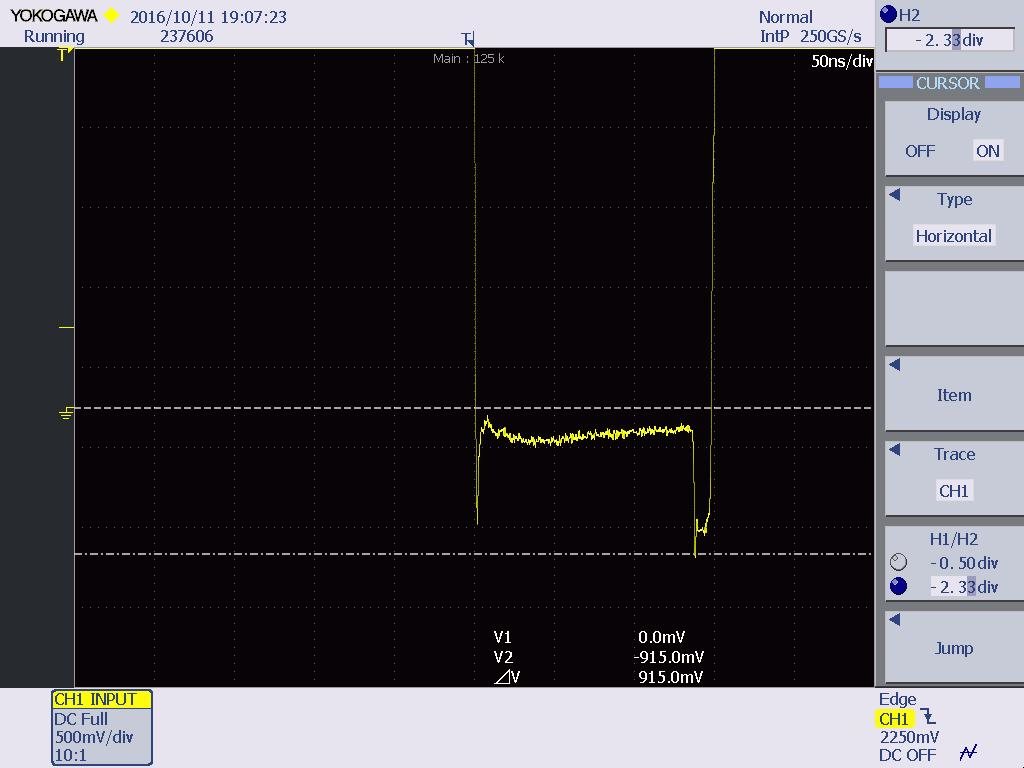

We probed the waveform & we observed the spike on switching node. By adding the snubber we are able to remove the +ve going spike but -ve spike are remains as it is.

Present layout is not good but it is not bad either. They have already made few changes to bring down the spike but after doing all the changes as per datasheet suggestions we haven't seen any improvement on -Ve spike.

Kindly find attachments of waveform & schematic.

-ve spike is around 900mV below ground & seems that it clearly violating the absolute maximum. Infect around the load current of 200mA spike is around -600mV & as the current increases up to 350mA it reaches to 900mV & after that upto 600mA output current it remains to 900mV.

Will this -ve spike creates any issue in longer run?

We need suugestions to improve on-ve going spike.

Regards,