Hi,

I'm having troubles using TI's LM5175. After cheking there's no error on the schematic, and since the nauture of the problem seems difficult to understand, I examine each part of the circuit separetly. First, I try to unferstand the BUCK converter branch.

This is the schematic (it has some probes defined in order to understand the further osciloscope captures).

The circuit is designed to drive up to 5A @ 12V.

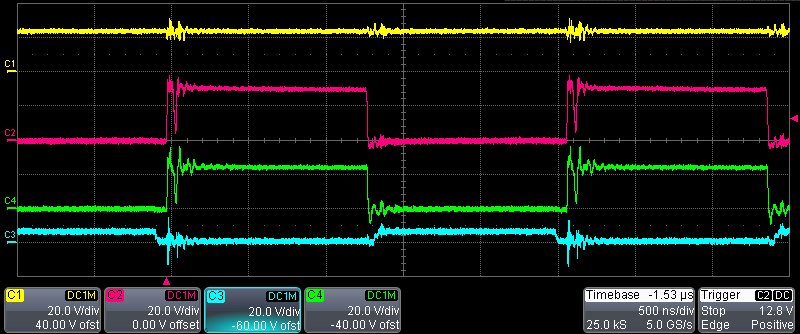

On BUCK phase, I get spected results as long as Iout is lower than 4A aprox. These are the corresponding waveforms:

It's worth noting the 2 step linear voltage drop on Gate and Source of the MOSFET (red and green probes) right after MOSFET's activation. I guess this is a clue of some of the missbehaviour.

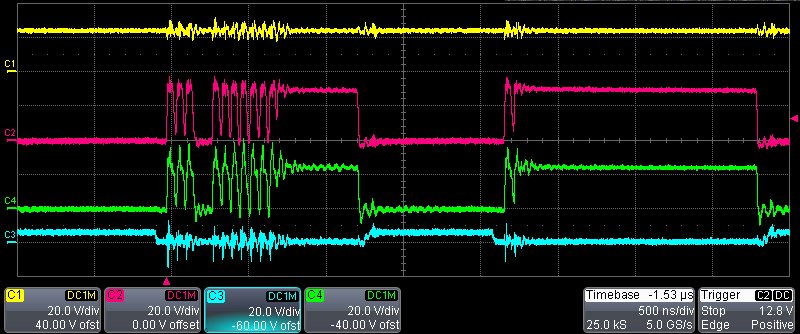

When Iout is approximately 5A, this is the corresponding waveforms:

This is a behaviour difficult to understand. It seems the Gate of the MOSFET is not able to mantain it's status during activation.

I would thank you all for some guidance or any kind of helpful information.

Best regards.