Please let me know about two points below of LM5574 maximum rating.

①Is there spec information of SW to GND transients?

For example, LM46000 datasheet page-4 described "SW to PGND less than 10ns Transients". (see below)

Customer want to know SW to GND transient spec of LM5574, too.

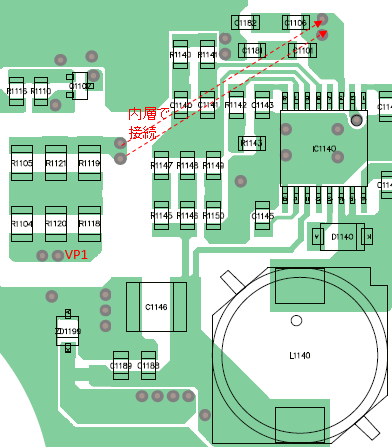

※Background is below, undershoot is -3.1V.

②LM5574 datasheet page-3 is described "SW to GND (Steady State)".

What mean of steady state?

Is this condition include undershoot?

Best regards,

Satoshi