Other Parts Discussed in Thread: TMS320C6678

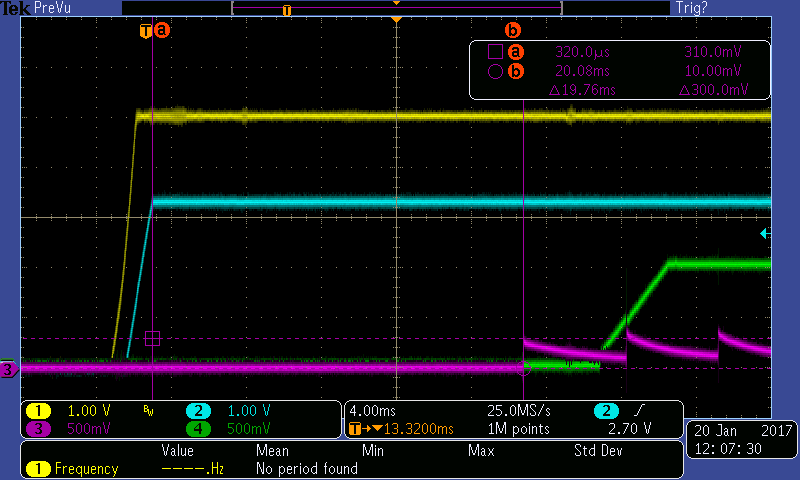

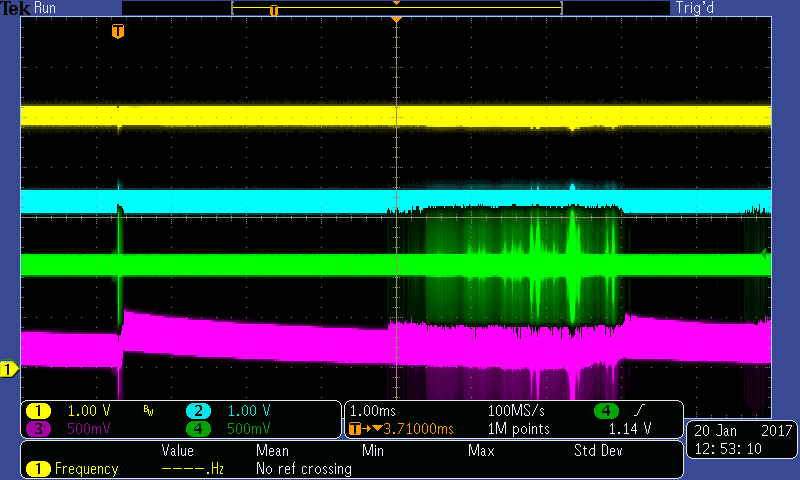

We are doing power cycle reliability testing on our TMS320C6678 design which uses a UCD9244 controller to bring up CVDD, 1.0V, 1.8V, and 1.5V (one accepted power-on sequence order according to the TMS320C6678 documentation). In about 5000 power cycles, we see 5-10 cycles where the DSP fails to boot. We have tracked this to the CVDD rail not coming up, and are unable to determine what is causing the problem. When the problem occurs, CVDD repeatedly attempts to come up, but it never does. However, 1.0V succeeds, which is a violation of the power-on sequence.

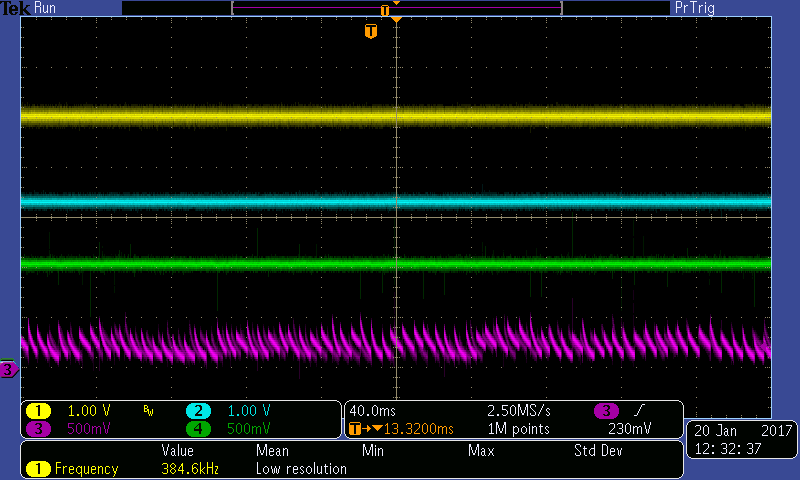

I've attached our XML file, a few scope captures, and some screenshots from the TI Fusion Digital Power Designer tool which were taken at the time of the failure.

This is a very edge-case scenario. We have seen this XML file fail on one of three boards at room temperature. When the two "good" boards are run over a -40 to +85C temperature profile while power cycling, they do not boot only 5 out of 6000 power cycles. The captures here are from the most problematic board of the three.

Is there a known bug with the UCD9244? Are we doing something wrong? Thank you for any insight you can provide on our issue.

Shown with infinite envelope, to show that the attempted ramp-up of CVDD is inconsistent: