Other Parts Discussed in Thread: UCC27201A

Dear All,

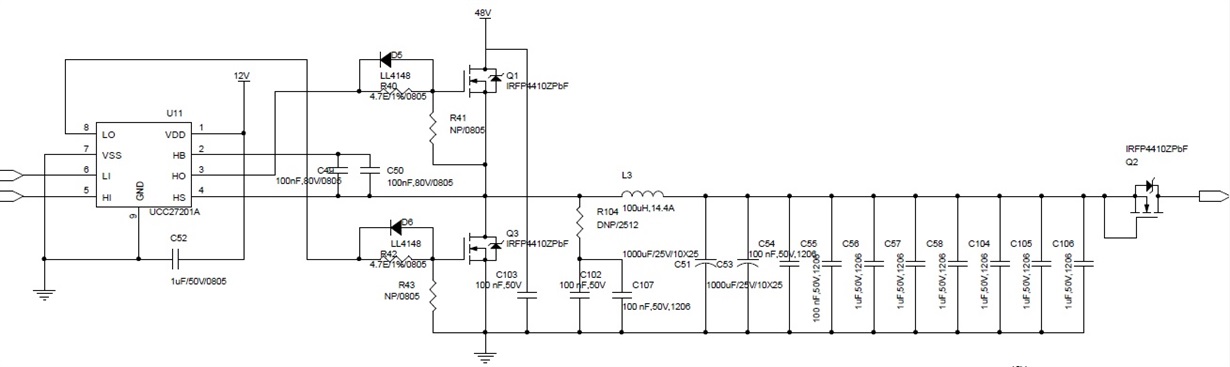

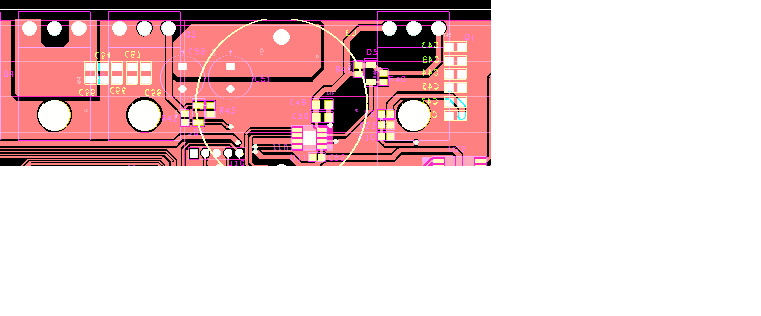

one of my customer using UCC27201A-Q1 part for battery tester product, they are facing some problem due to UCC27201A-Q1 with thermal pads.

1. At long run the IC gets hot and fails. Wondering if thermal pads are any issue.

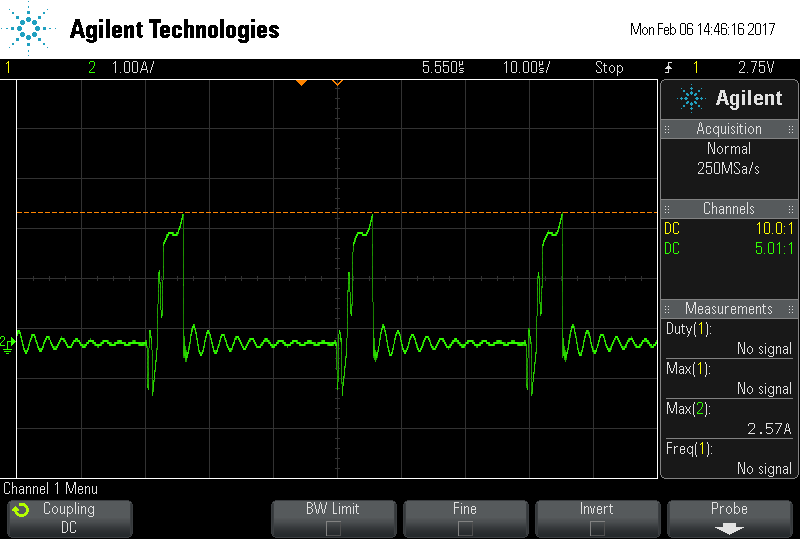

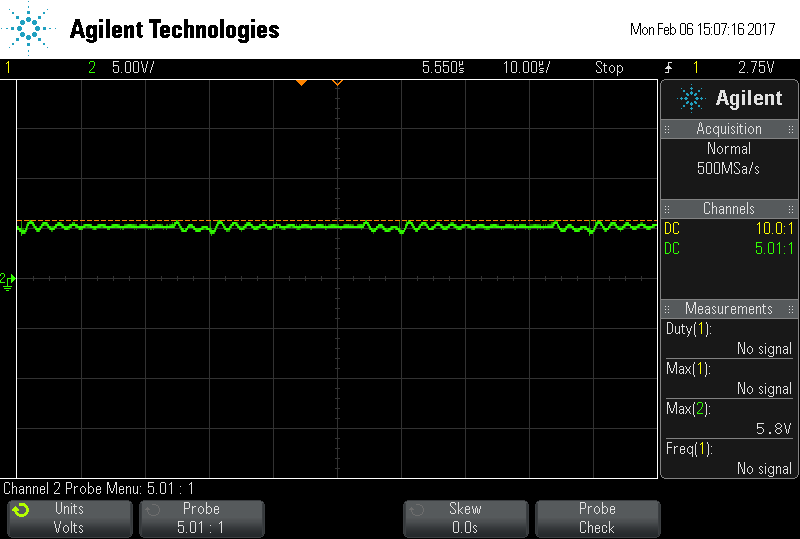

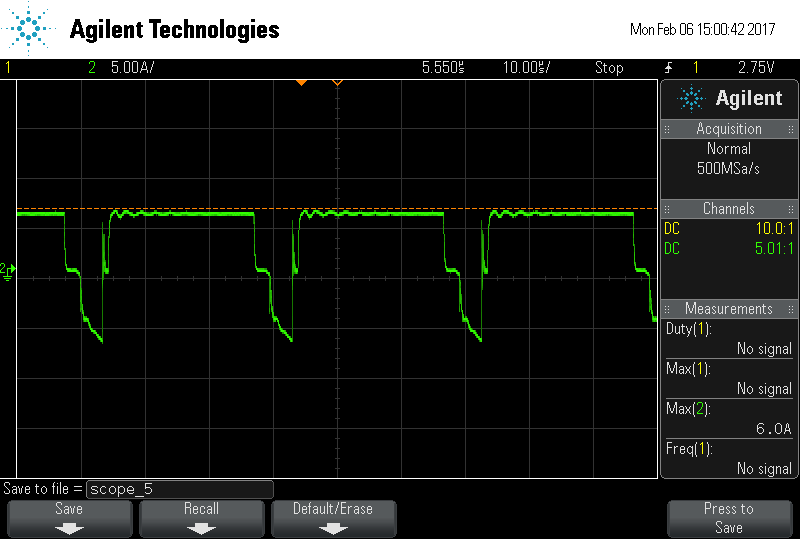

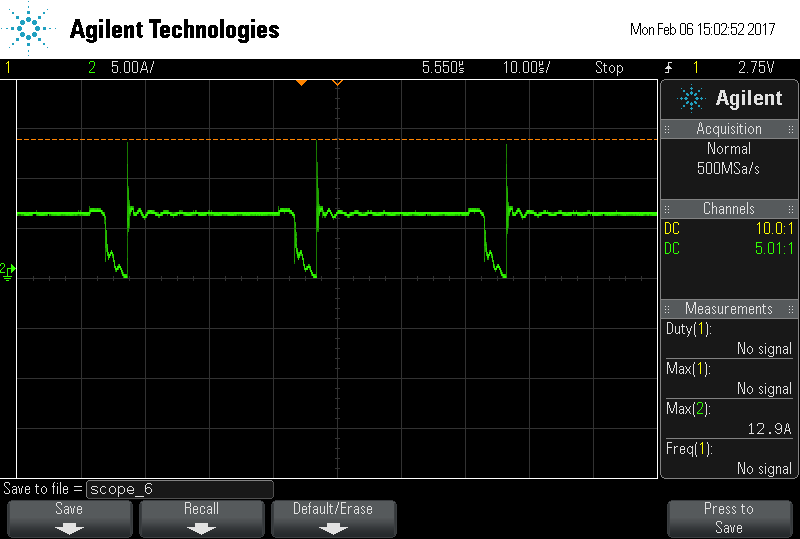

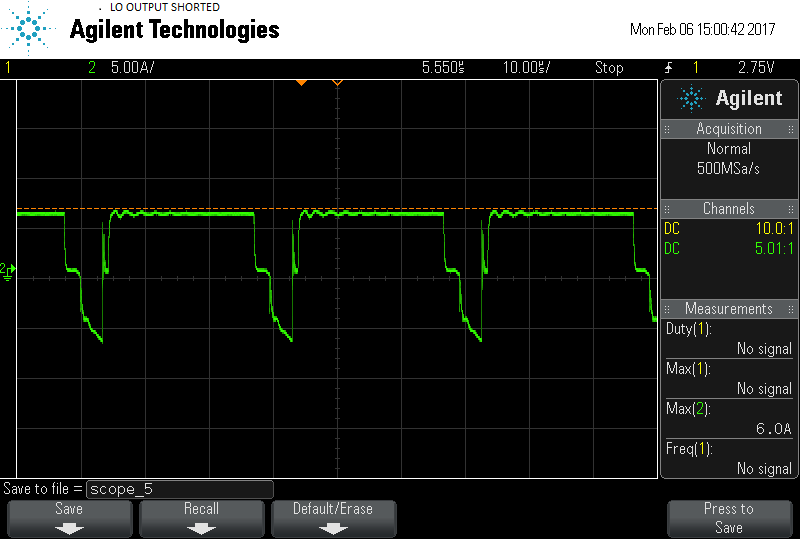

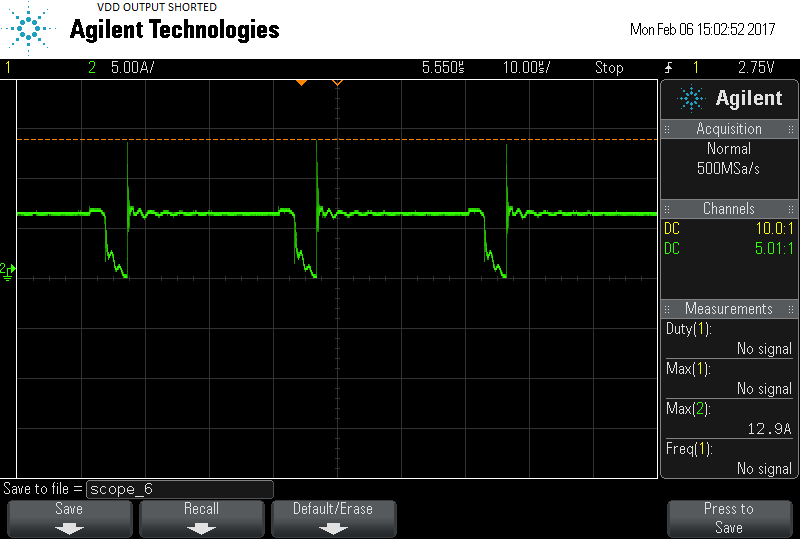

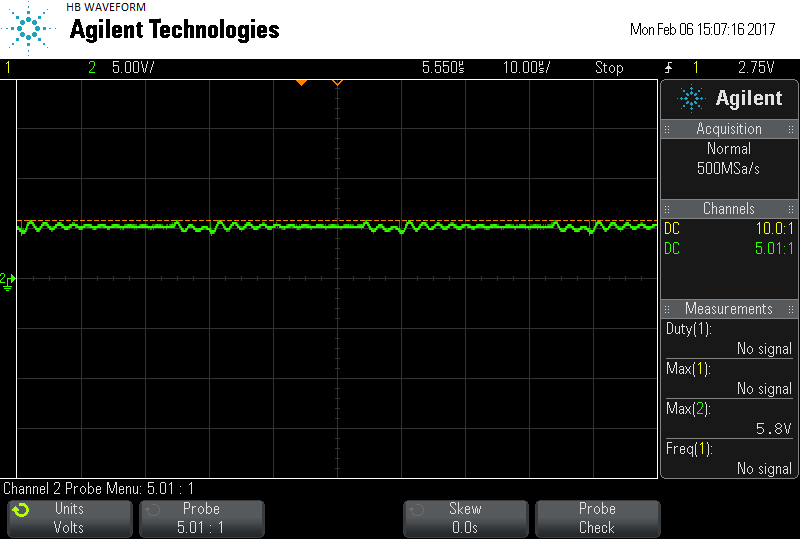

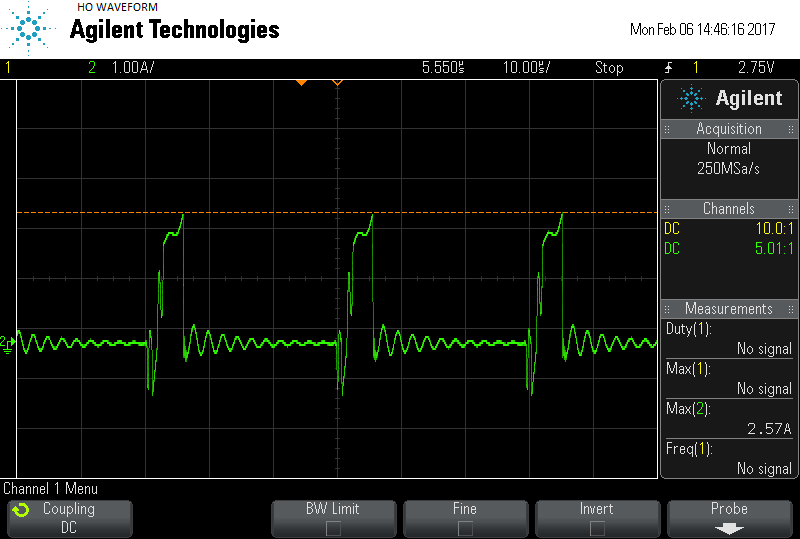

2. If the output of this synchronous buck converter is terminated by very small resistance (say fully turned on MOSFET with resistance of 40mOhm) the gate of high side MOSFET draws huge currents like 1.8A. Couldnt figure out this behaviour.

Request you to advise your feedback.

Rgds,

Aravind.