Other Parts Discussed in Thread: CSD16321Q5

Tool/software: WEBENCH® Design Tools

Hi,

Having rather rare issues in cold temperture (-40c) with the tps40304 design.

Also in is are the MOSFET (CSD16321Q5) as the lower and upper FETs.

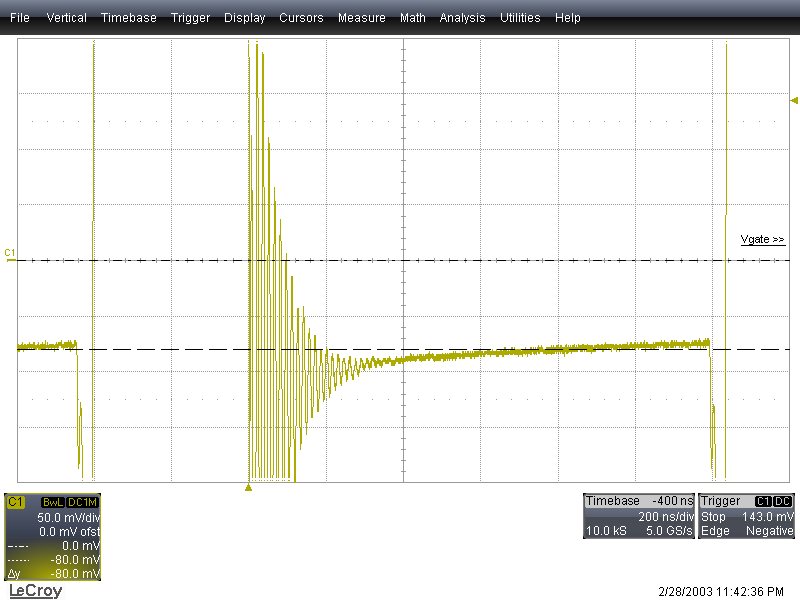

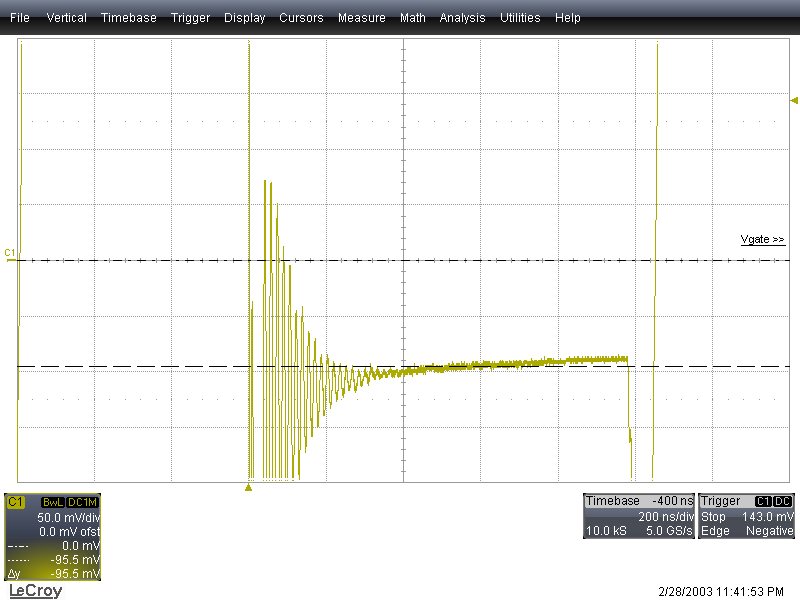

The output voltage (1.0v)is dropping (few second after power up). Input voltage (3.3v) is stable. probbing the SW pin, and pulses are ceasing (No pulse signals).

It looks as if the VRM is shutting. Enable pin is "ON".

I tried to increase the OC resistor. Works (failure not duplicated) on one board, failing on another board.

I have noticed that both contorller and MOSFET datasheets we updated in 2016 (the design was based on older datasheets).

How can i confirm i have an OCP condition? i cannot measure the output current , with the current setup (theoretical analysis shows that i am not in over current issue).

Could there be other reason for VRM shutdown?

P.S. On the first failiure occurence, the tps40304 and mosfet were replaced. failure was not reproducible after that. (and as i said this is a rare failure).

Thanks,