Hi team,

My customer is using TPS54394 in their project to power up FPGA. They want to use power good pins and EN pins to achieve power up sequence management.

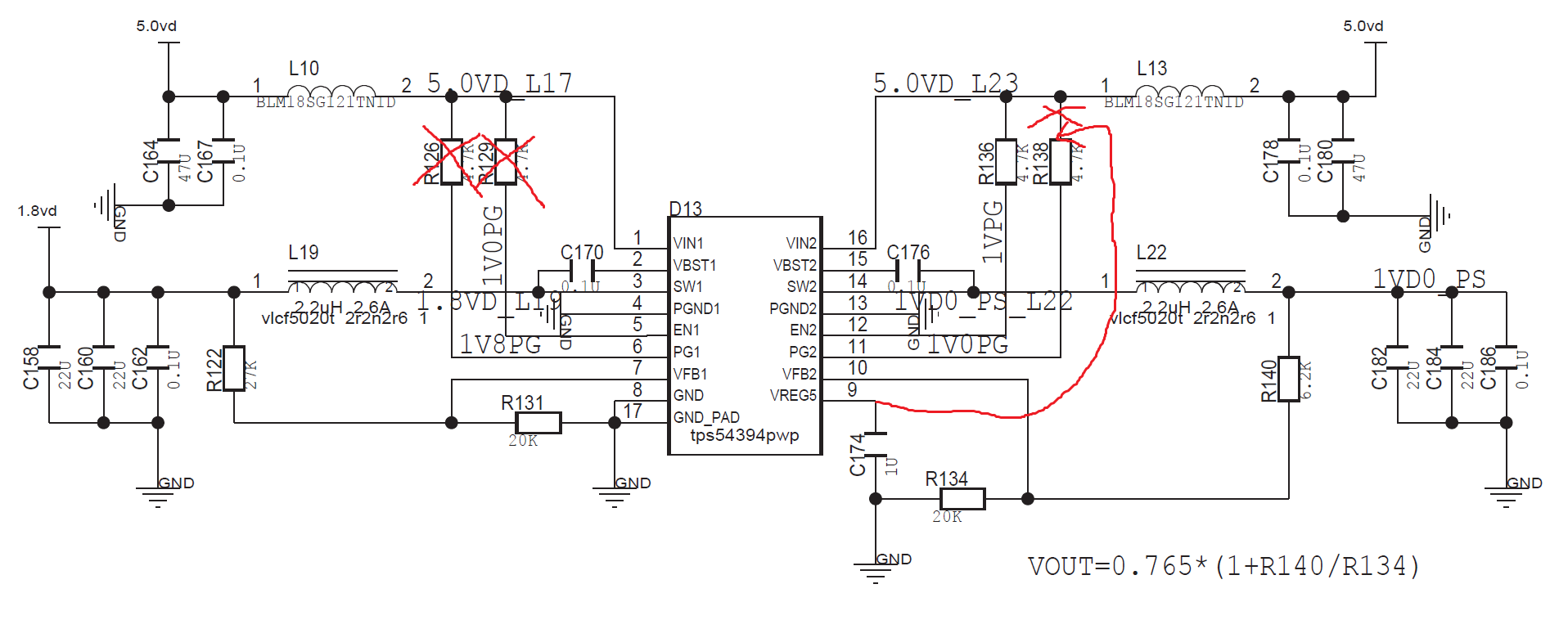

The schematic is as below. The red line is some debug changes.

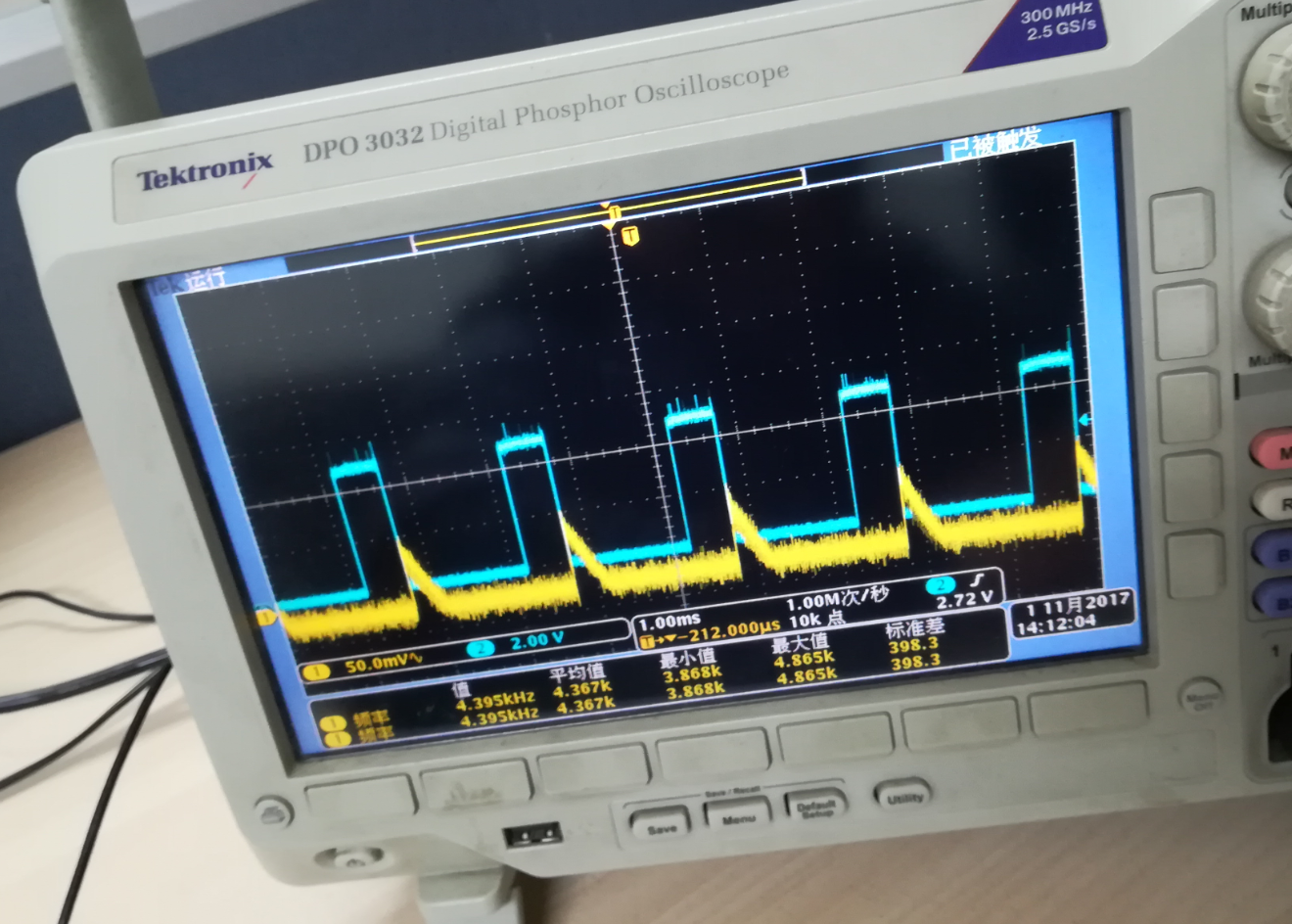

Input voltage is 5V, Vout1 is 1.8V, Vout2 is 1V. Use PG2 to control EN1, R129 removed. PG2 is pull up to VREG5 through 4.7k resistor. PG1 left floating, R126 romeved. However the output is abnormal. PG2(Bule) and Vout AC coupled ripple(yellow) just as figure 2. The power good is not good now.

If I disconnect PG2 to EN1, and pull EN1 up through 4.7k resisitor, the output voltage has no ripple and PG2 out high.

I don't know what wrong with this schmatic. Could you give some comments? How should we use power good pins and EN pins to power up sequence management in TPS54394?

figure 1

figure 2