Hi

My customer has some query need help.

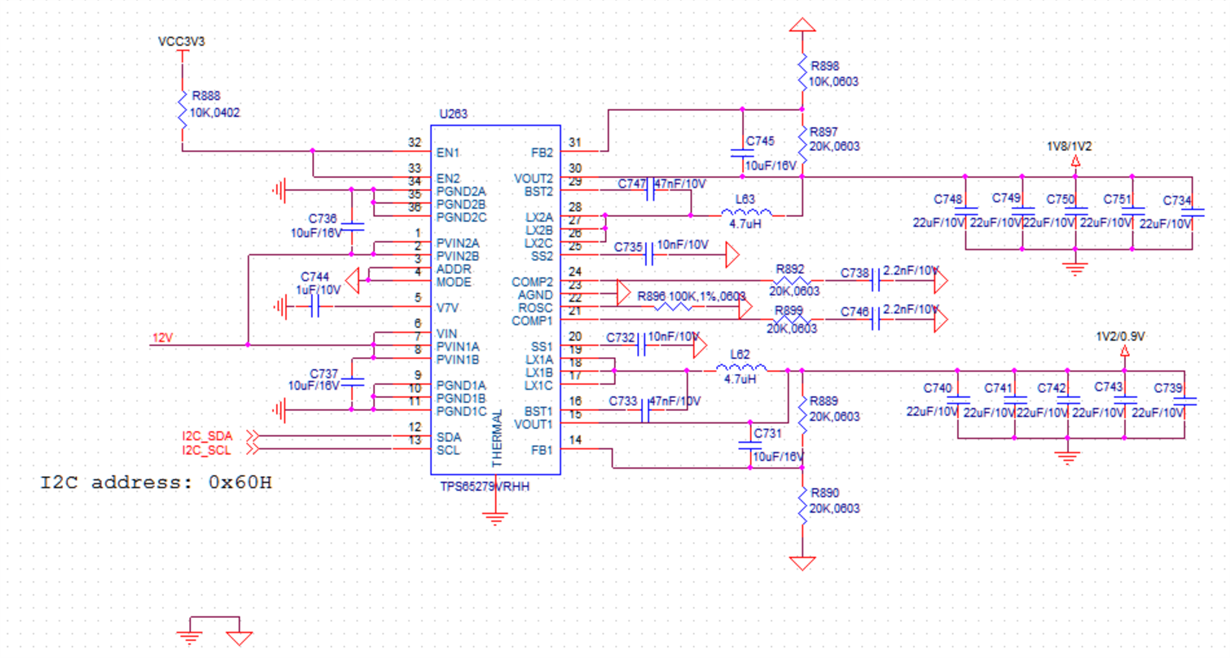

The issue is when using TPS65279VRHH power management IC on our development board.

We are using 12V as VIN, and expect is 1.8V for VOUT2 and 1.2V for VOUT1, which we currently using the resistor mode to configure these 2 outputs. .

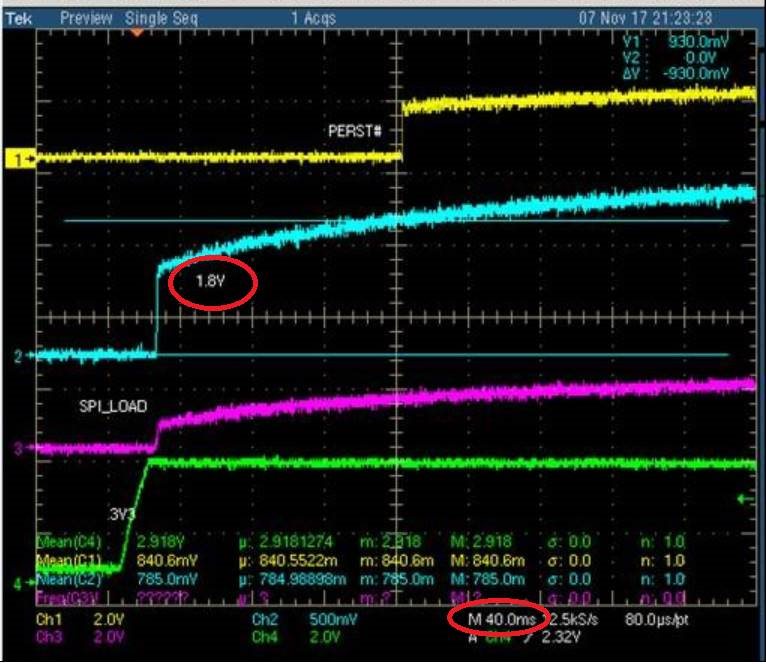

According to our spec, we need VOUT ramp to 1.8V/1.2V within 25ms after VIN enabled. But actually we measured it took more than 600ms when VIN was enabled. Waveform is as below. Blue one is the VOUT 1.8V, which should be compared to 12V VIN but in below waveform the green one 3.3V is also OK for comparison as it has the same timing sequence with 12V VIN.

Please help check and feedback your suggestion.

thanks

Star