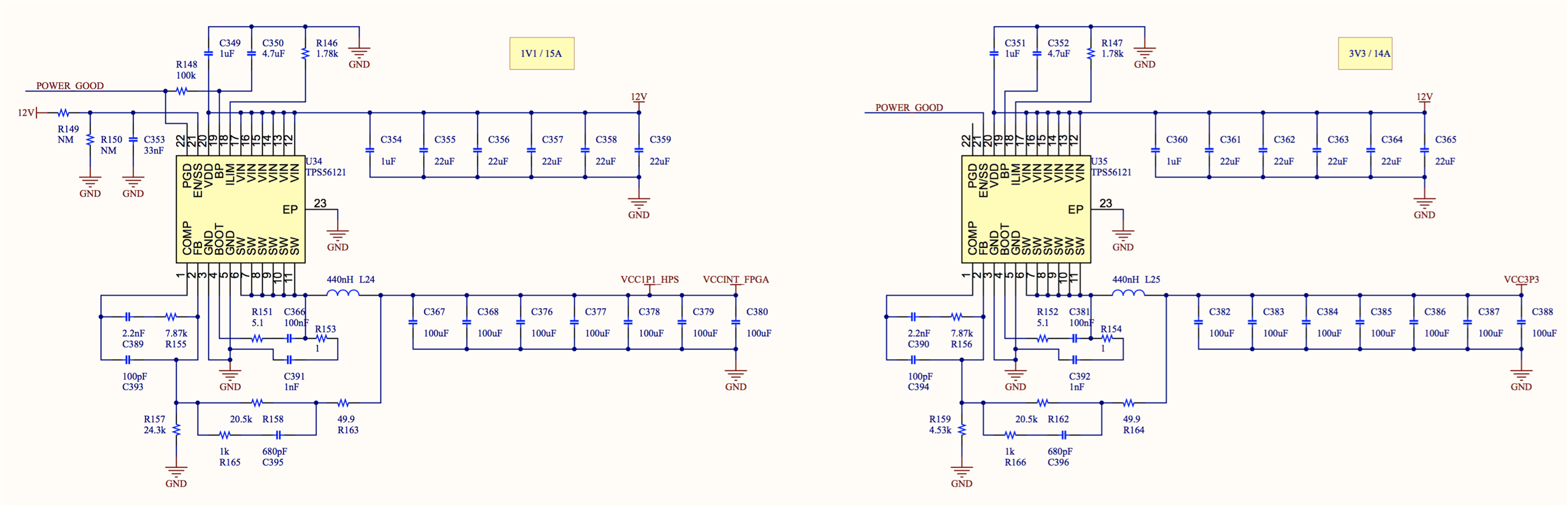

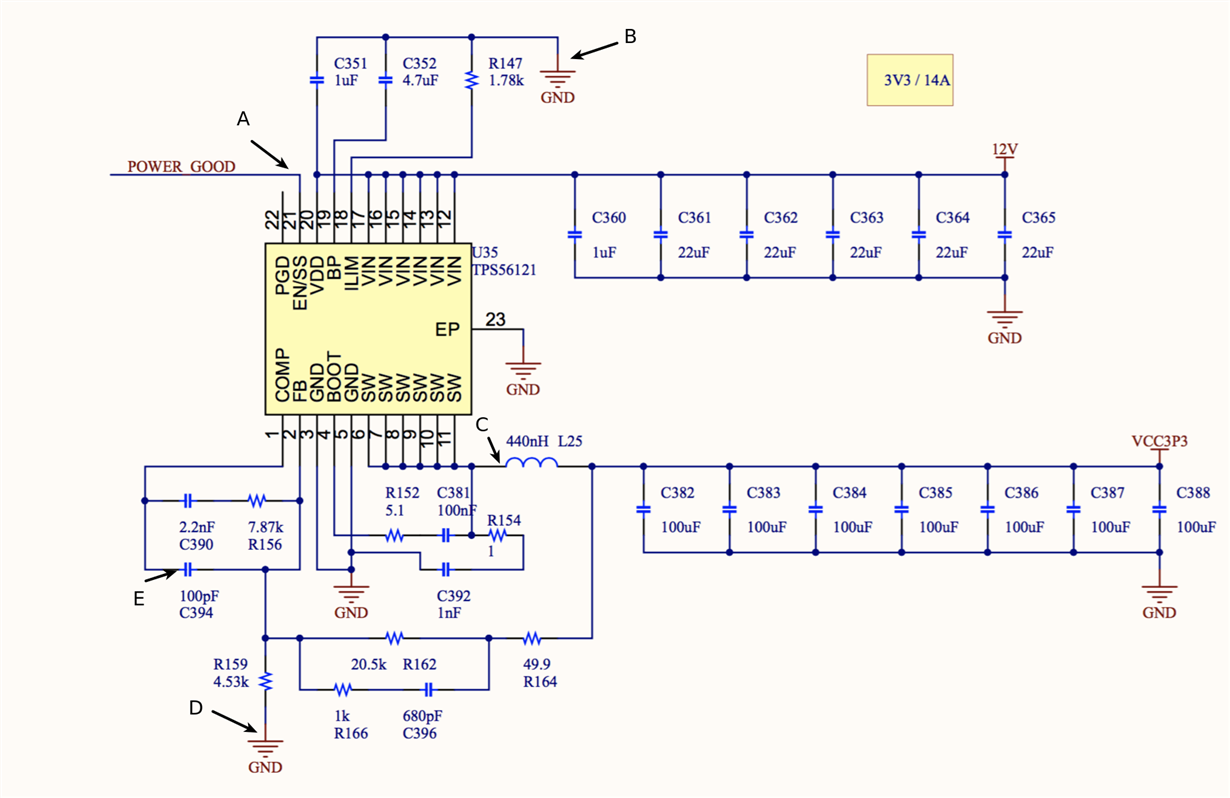

We are facing a serious device failure when powering a TPS56121 with 12V. The device somehow breaks and forwards the 12V to its output, thus burning all the ICs on its output power rail. The device is configured to output 3.3V up to a maximum of 14A and it is enabled by another TPS56121 that generates 1.1V@15A, which seems to work properly.

We are having difficulties in understanding why this happens because it happens randomly. We have inspected carefully the PCB and it seems that there are no issues in manufacturing.

I'm attaching a schematic drawing of the TPS56121, is there anything wrong?