Hi

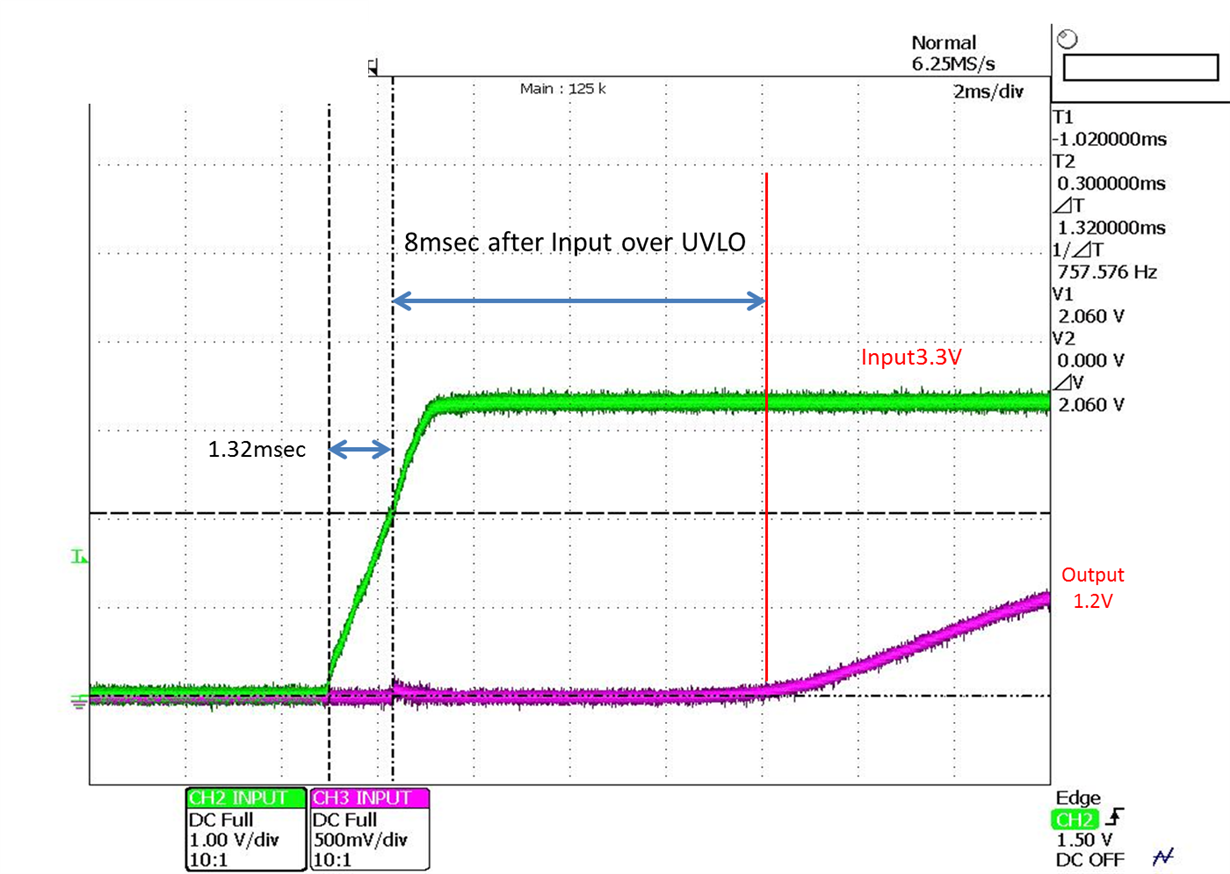

I have question about start up delay.

I'm referring Figure 29 from datasheet.

The circled point represents start up delay (~60msec).

Is there variation of this delay?

For example, is it normal if the delay would be 2msec?

I assume 3.3V to 1.2V regulation.

BestRegards