Hi Team,

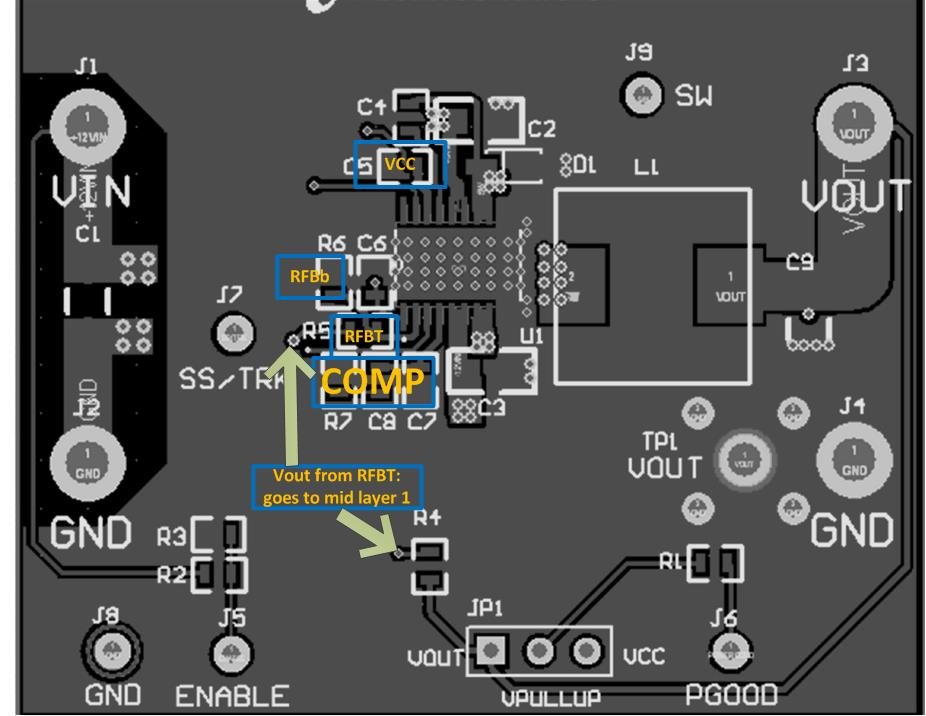

Please find attached design I did for 3.3V output and 5V output from 15V and 5V input.

I designed error feedback for correcting the voltage output in 2 options .

- With OP Amp .

- With resistor divider that get the voltage from Vesnse instead of output voltage.

The ripple is very high and when using the OP Amp is even worse.

Please advise.

Best regards,

Shlomi