Hi,

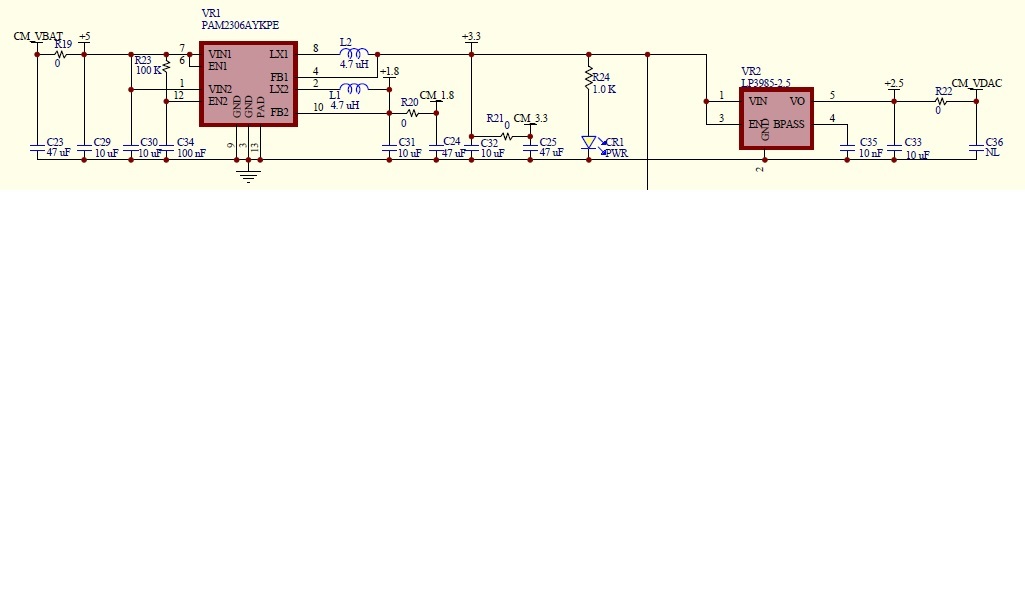

I am debugging a new design that uses the LP3985-2.5 to power a FPGA. The same FPGA also has banks running on 3.3V. I have a series 0 ohm resistor between the regulator and FPGA so I can disconnect the FPGA load leaving only the output capacitor. There is 10 uF in parallel with 47 uF on the input of the LP and 10 uF on its output. There's a 10 nF between bypass and ground. I have two prototype boards. Originally there appeared to be a short between 3.3V and 2.5V (under the FPGA, of course). I removed and replaced the FPGA and the short is gone but I am using the same LP3985-2.5. With its output now disconnected from the FPGA but still connected to its output capacitor, the LP input measures 3.359V and its output measures 3.216V. I have a second board whose LP3985 output was originally attached to the FPGA and measured 3.3V, so i removed its zero ohm jumper. Disconnected from its load the second board's LP3985-2.5 measures 3.24V with its input measuring 3.28.

So it is possible on the first board, the LP's output was being dragged above it's nominal 2.5V output value. From the simplified block diagram, this wouldn't appear to damage the LP since it cannot sink current if the output is pulled above its regulation value. On the second board, however, there is (and was never) a short, so it is difficult to explain how it is no longer regulating. I have attached the schematic sheet.

Any thoughts are most appreciated.

Thanks,

Scott