Other Parts Discussed in Thread: LMR14050

Support Path: /Product/Development and troubleshooting/

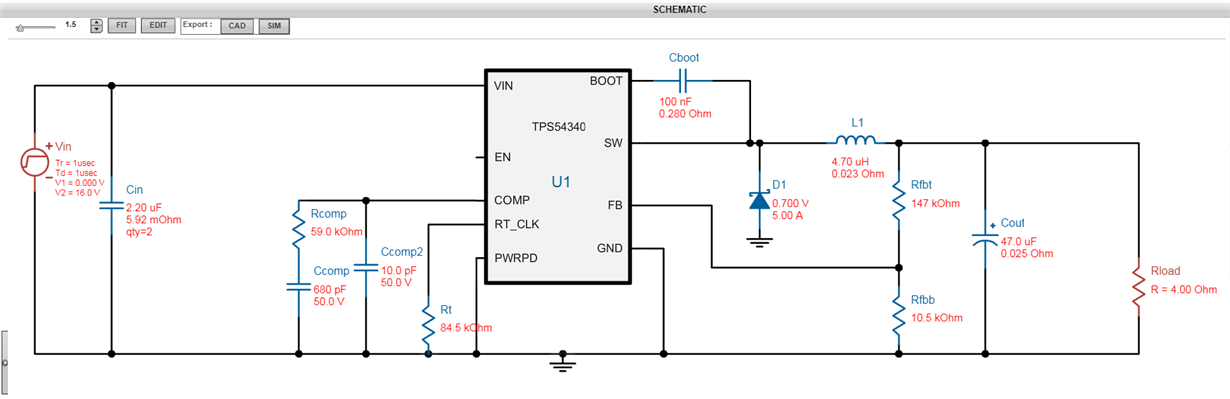

I am using the TPS54340 to provide +12V, 3A with a Vin of 14-18V.

I used WEBDesigner and built the 5 PCBs using the design. They marginally work when starting up with load of 1-3A.

The symptom appears to be output skipping - I added ULVO to not start until I am above 14.5V - that help get the plots provided.

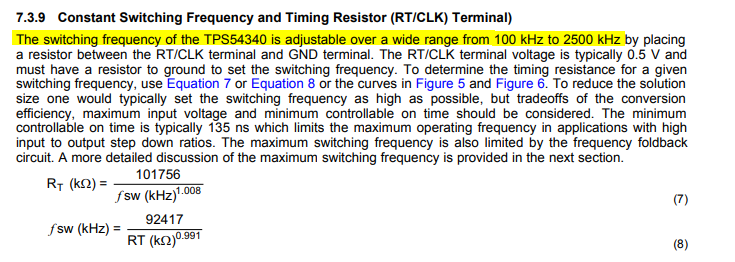

The datasheet calculations suggest a max Freq of 330 kHz but the WEBDesigner provided 84.5k for ~ 1MHz.

I suspect it is frequency related but don't know why WEDDesigner can be so misleading. FYI if you put the design example in the data sheet into WEBDesigner it violates the rules also.

Adrian