Other Parts Discussed in Thread: UC1825,

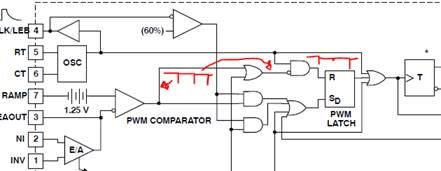

I have experienced some problems with the UC3825 when operating at low duty cycles. The device controlles a symmetrical half-bridge converter, oscillator is set to 380kHz, LEB is set to minimum (by connecting a 2k15 without any capacitor to the LEB Input). The RAMP-Input is feed with a slope compensation signal and a small amount of the transformer primary current (Peak current mode). The soft-start (pin o/c) and ILIM - function (voltag is <200mV) is not used.

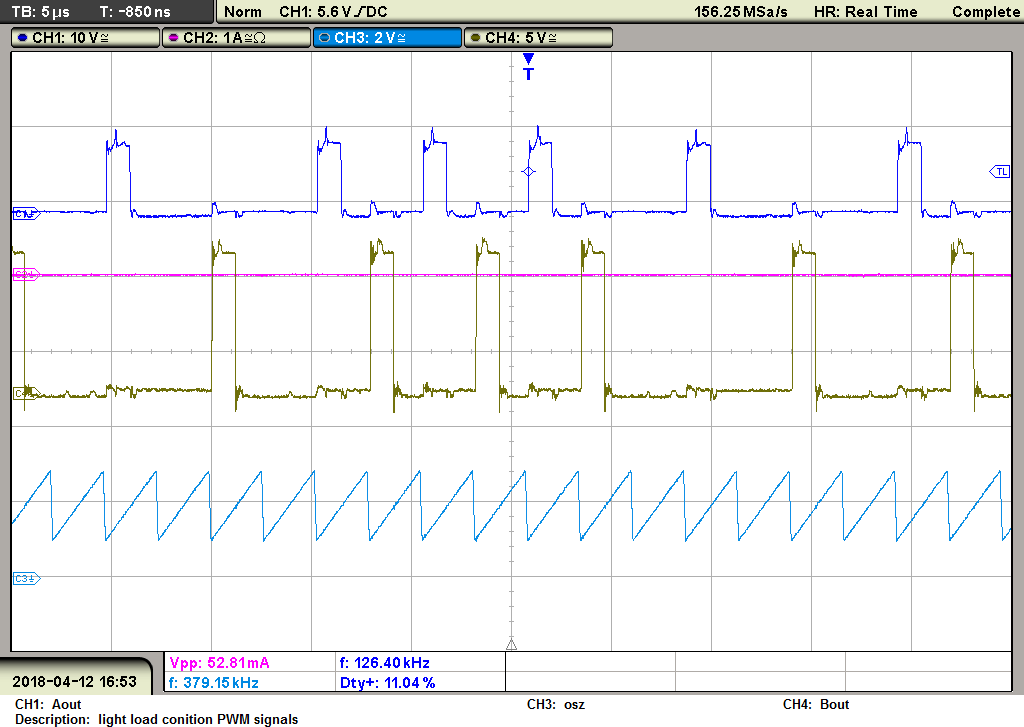

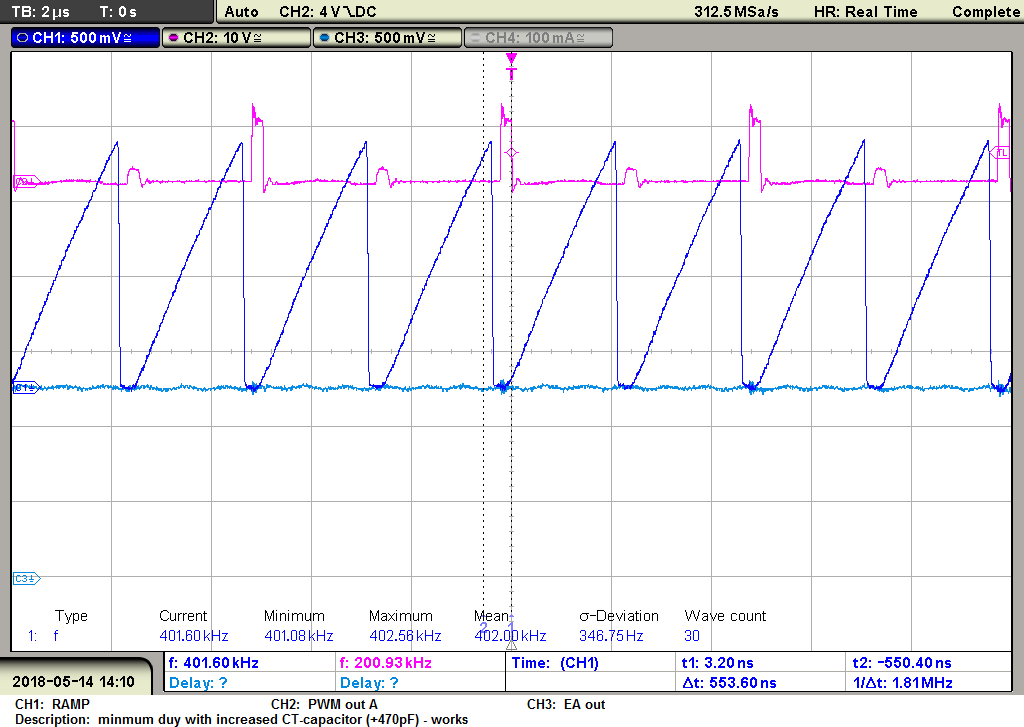

The device operates as expected under medium to high load conditions where the converter operates in continous conduciton mode (duty cycle per output is arround 30%). Under light load conditions discontinous conduction mode takes place and the duty cycle is reduced. In this condition the minimum duty cylce stucks arround 20%. If lower duty cylce is needed, some pulses on the Aout or Bout output are suppressed completely. It also looks like the internal toggle-flip-flop is toggling unindentional. The effect also leads to an audible noise since the AC-voltage applied to the transformer primary is disturbed.

Here is a typical measurement:

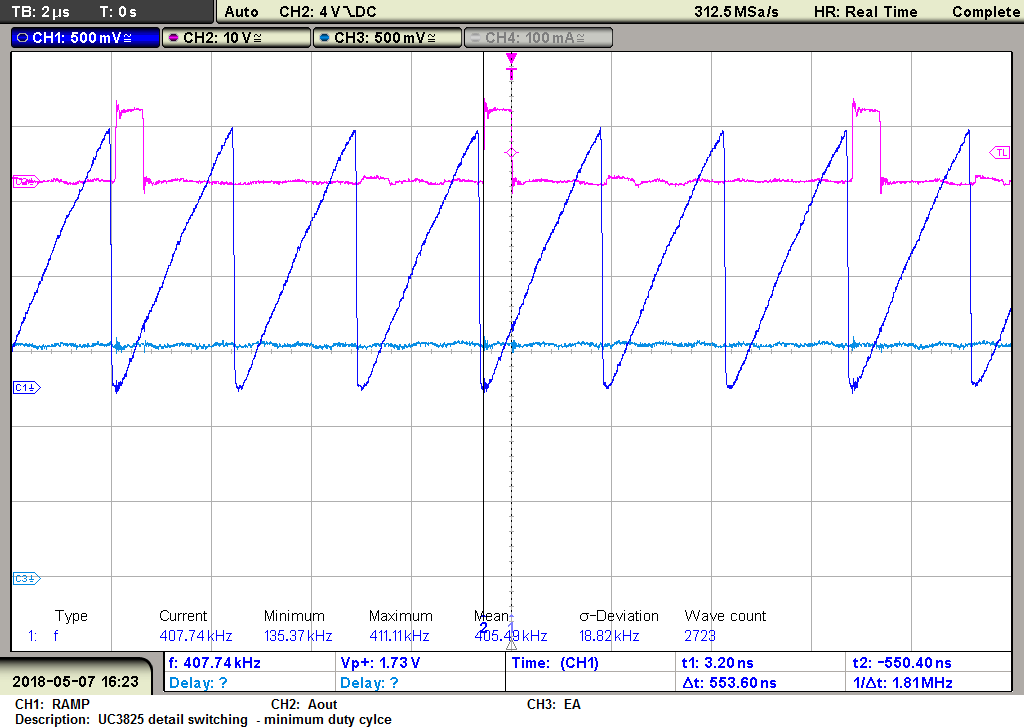

I have modified the circuit by applying pure voltage mode (as shown in the datasheet /app note) by connecting the CT and Ramp Input: The same effect but slightly lower duty cycles have been reached.

I also reduced all kind of EMC-influence by shielding and filtering of supplies and other signals -> no effect.

Lower minimum duty cylce has been reached by reducing the source impedance of triangular signal applied to the RAMP-Input - but the effect is still visible.

The datasheet does not give any information of minimum duty cylce (it is stated in the text that Zero duty cycle is possible); also no Information about required source impedance of the RAMP-Input.

Is this effect known? Is there a work-arround?

We currently use the UC3825 for the breadboard - but we want to use the UC1825 for the product. Would it be the same for the UC1825?