Other Parts Discussed in Thread: TM4C1294KCPDT,

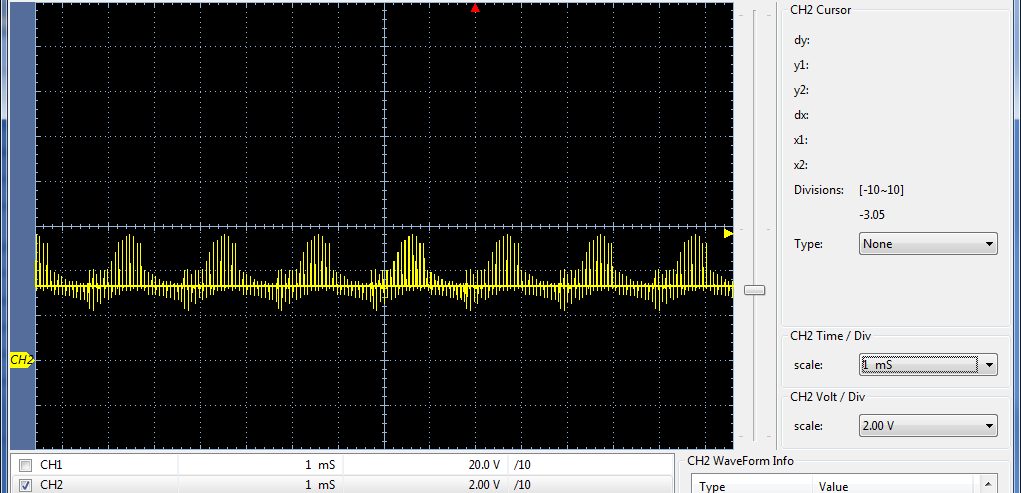

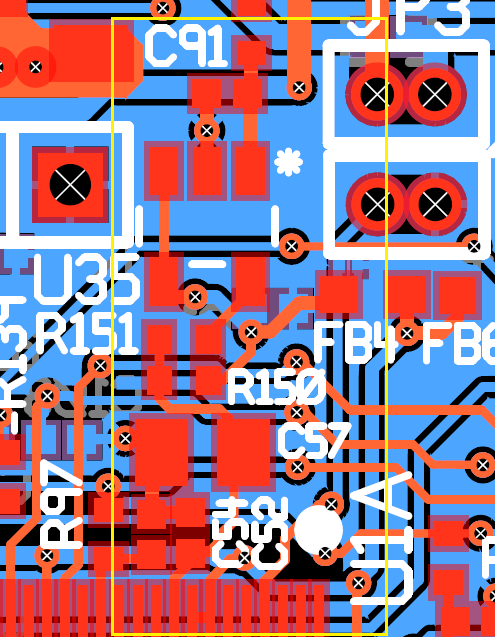

Hello we are capturing far to many PWM pulses on output pin 5 and wonder if bypass C104 or sourcing AGND from VIA's may lead to poor PWM noise rejection?

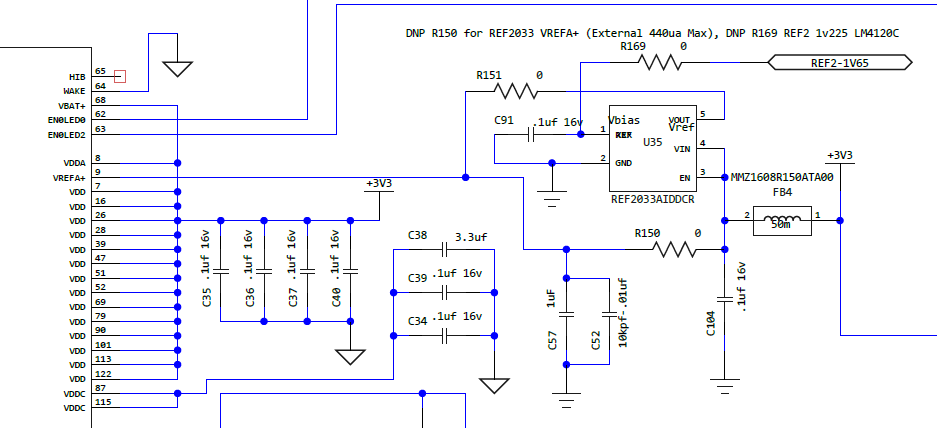

Notice C57 & C52 are required per MCU datasheet (TM4C1294KCPDT) ADC0 electrical specification for use with external +VREF. R169/150 are not populated.

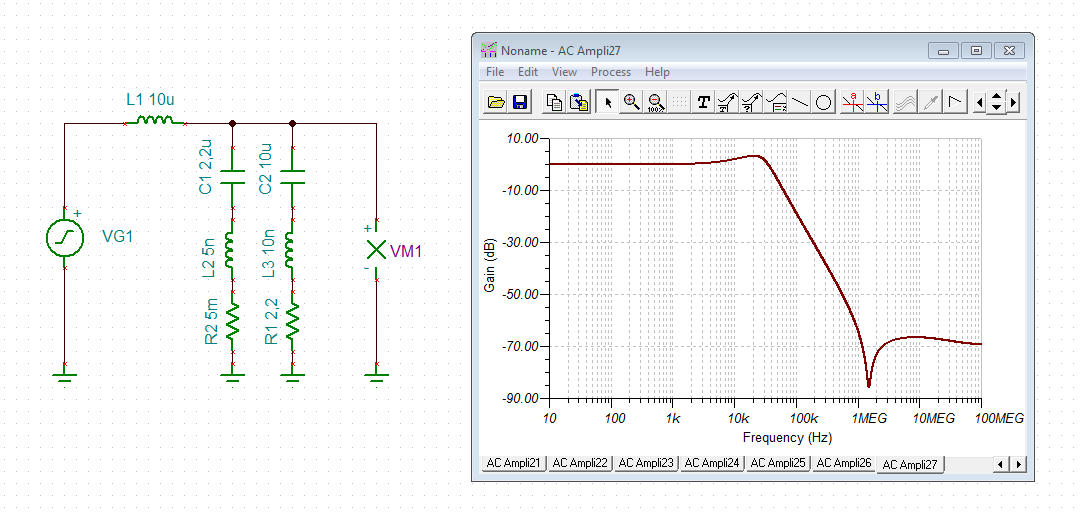

The MCU internal VREF produces clean ADC samples without much if any 12.5Khz PWM spikes showing up in GUI scope widgets. What can be done to improve REF20333 circuit to stop PWM on pin 5?

Thanks in advance for constructive ideas.