Other Parts Discussed in Thread: UCD90SEQ64EVM-650, SEGGER

We have a problem with some of our boards using a UcD90120A:

The problem is seen on 6 of 100 boards. The remaining 94 boards are working fine

5 of the 6 boards are newly produced, but the 6th is the one I have been using to get the configuration right on the UcD90120A.

On the 6th board the problem occurred after a reprogramming of the configuration by JTAG.

We use JTAG to program the boards.

We are using I2C at 400kHz. the pull-ups are 1kOhm.

The ADDR resistors are both 90.9kOhm giving the I2C address 0x68.

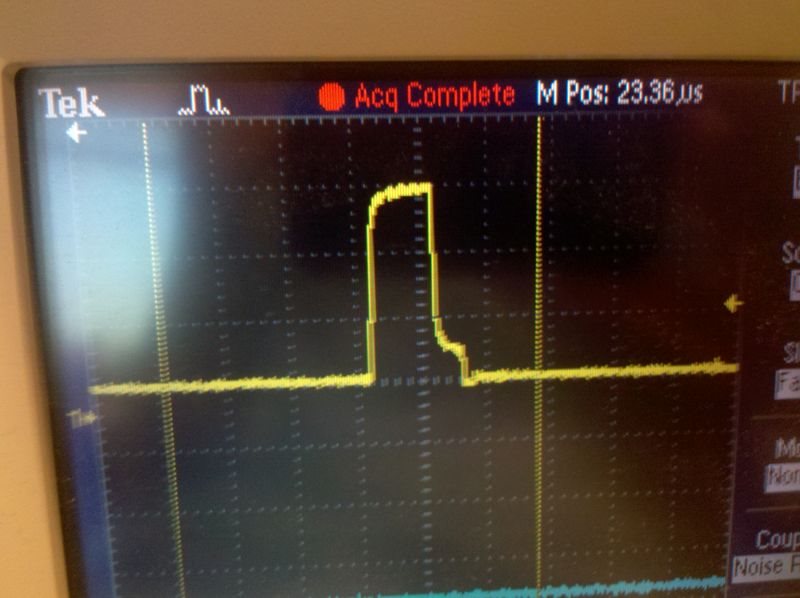

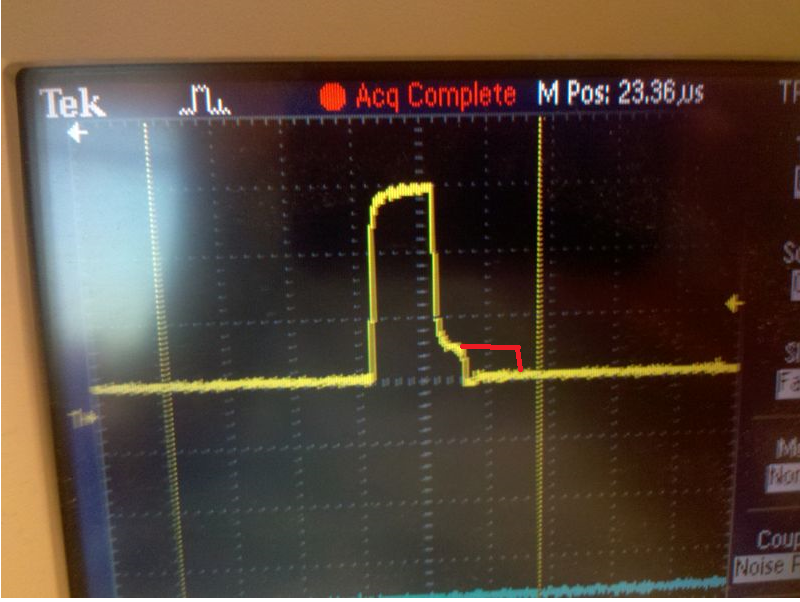

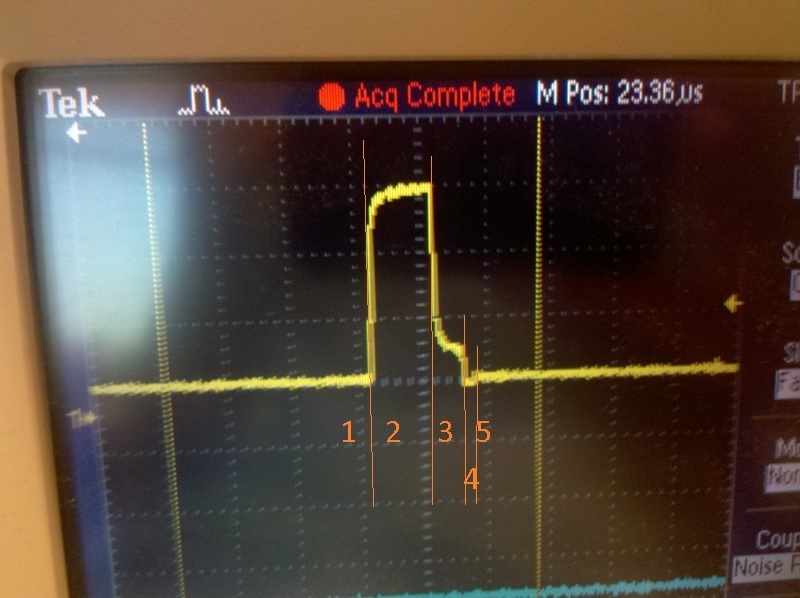

What I can see from scoping the SCL/SDA is the SCL is pulled low by the UcD90120A just (0.2us) after the 9th rising edge of the access (in the middle of the ACK/NACK) regardless of the address sent on the I2C bus.

I can see that the SCL is first pulled low by the UcD90120A and then 50ns later by the I2C controller and held low for 1.25us before the I2C controller continues generating 400kHz clock pulses.

Any idea what I can do to fix these boards?

I have tried to reprogram the firmware via JTAG, but that doesn't solve the problem.

Regards,

Søren M.

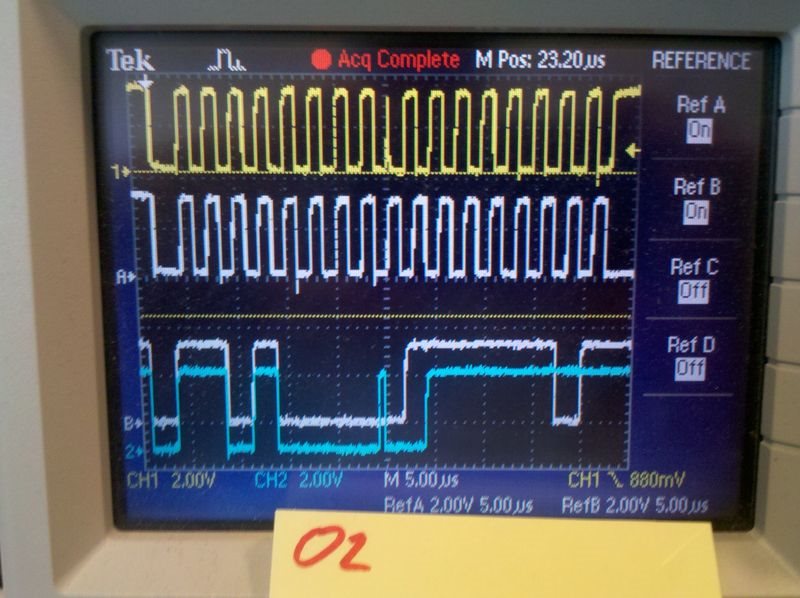

Scope shot: (Yellow: SCL, Blue: SDA, White: Reference from working board)