Dear E2E:

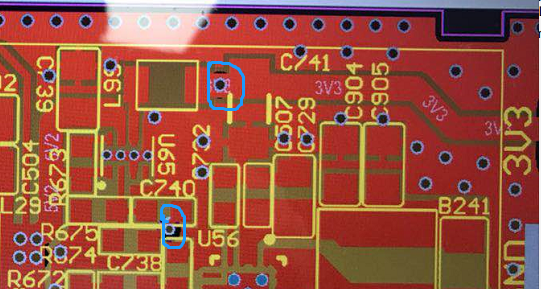

Compared to the schematic and pcb layout, i found the via near L99 in wrong position, i should be behind the output cap C741.

The input cap C739 was not very perfecter.

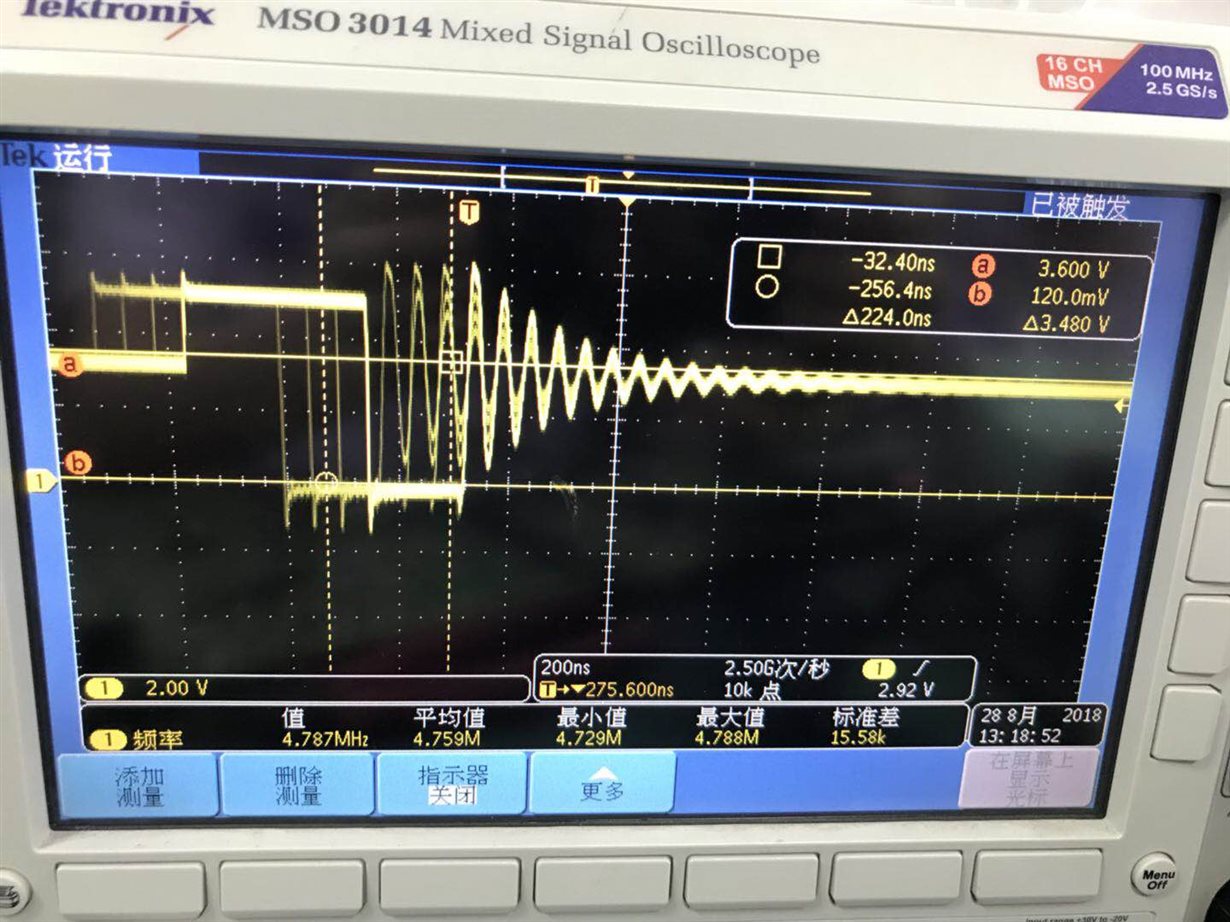

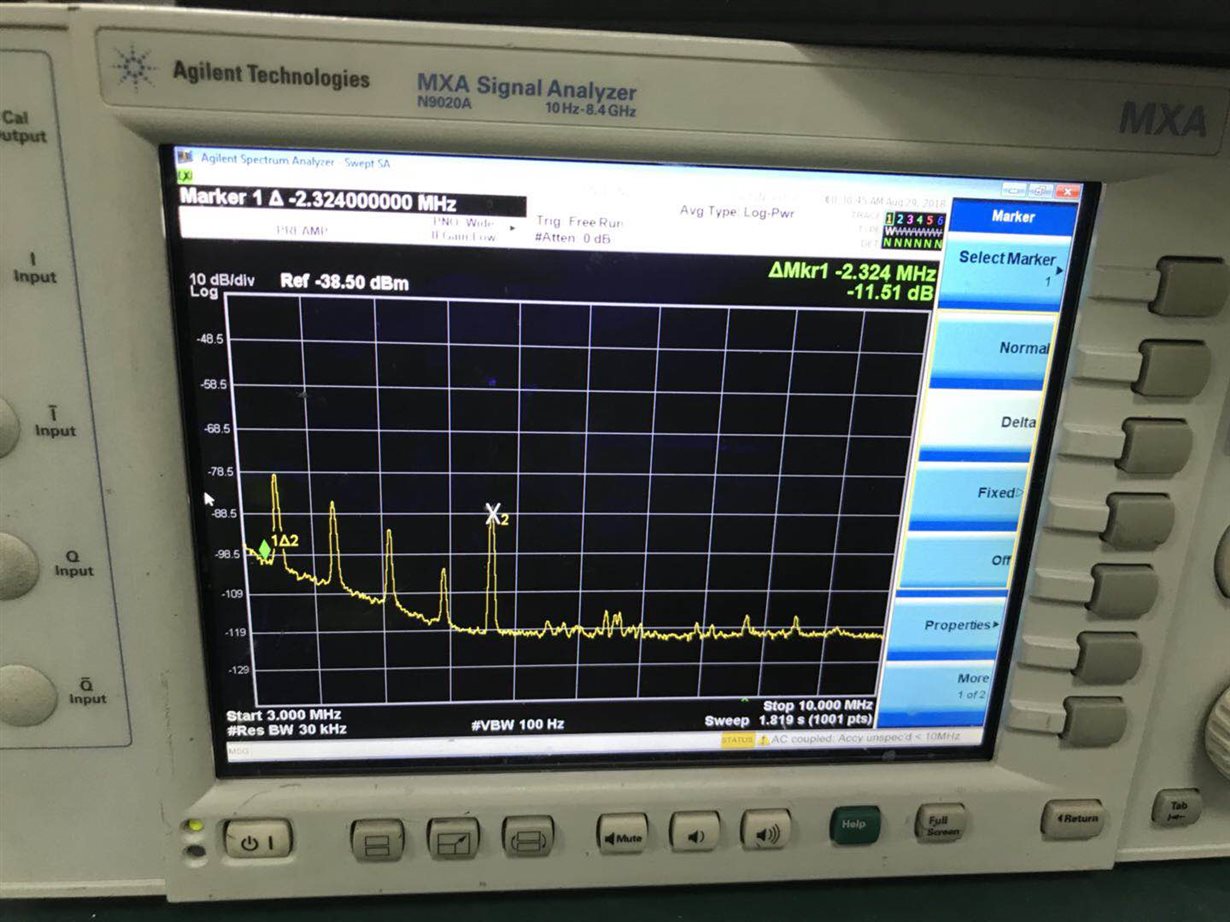

I check the sw waveform, it's bad. The output point waveform through Spectrum Analyzer is not very good too.

I have no idea how to improved the performance, now i add a ferrite bead in sw point.

may i know your suggest ,thanks

Spectrum Analyzer Waveform:

Customer schematic :

PCB Layout: