Other Parts Discussed in Thread: TPS43351-Q1

Hi Again,

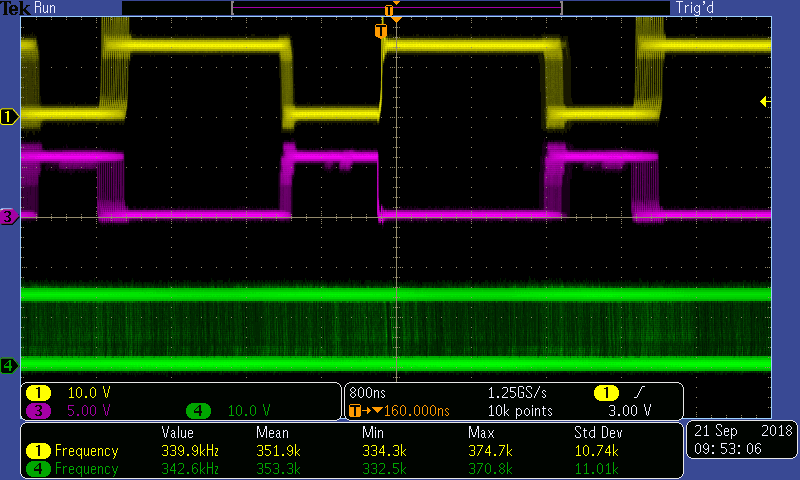

I'm asking this question now because I wanted to be sure that frequency synchronization issues were not at fault. Now that those are resolved, I have the same circuit, now the output #4, Gordion has the complete schematics. For VIN above 12.0V and Iout above 3.5A, I see a progressively worse sub-harmonic osculation in the switch node duty cycle. Increasing VIN and/or Iout make this oscillation more and more pronounced.

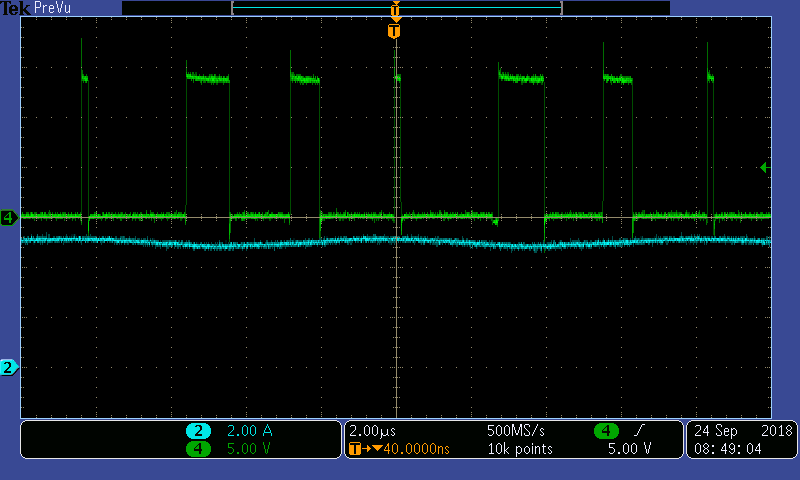

Ch.2 = Iout, Ch.4 = SW node, this is for VIN = 13.8V and Iout = 5A (max load)

My first post about this IC led to two changes with the first TPS43351-Q1 on the board, those were to remove the resistor that connected the other output which is 5.0V to the EXTSUP pin and to increase the VREG pin capacitance to 4.7 uF. I have made those two changes to the second TPS43351 that generates this 3.3V, 5A output, but neither has stopped the oscillation.

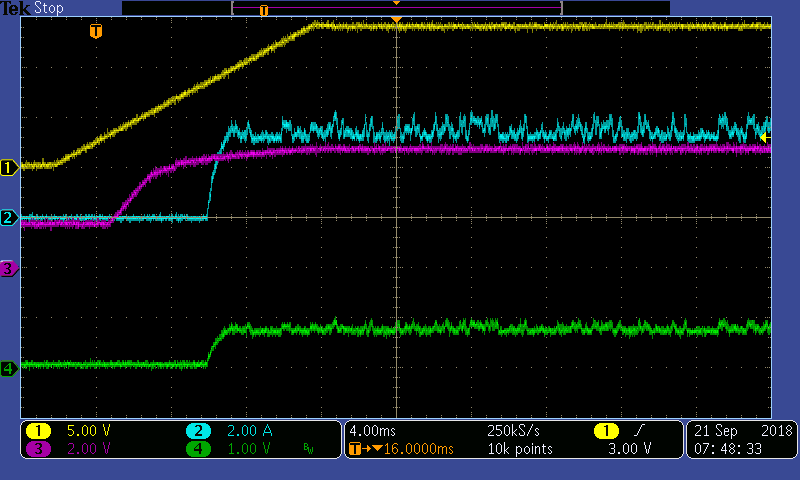

In addition, I found that if I tried to start up into a load higher than 3.5A (constant current load), either by applying input power or by using the logic enable, the output would get stuck with a voltage of around 0.8V and delivering those 3.5A of average current. Here''s a plot of such a startup:

Ch.1 = VIN, Ch.2 = Iout, Ch.3 = ENA and ENB pins, Ch.4 = Vout

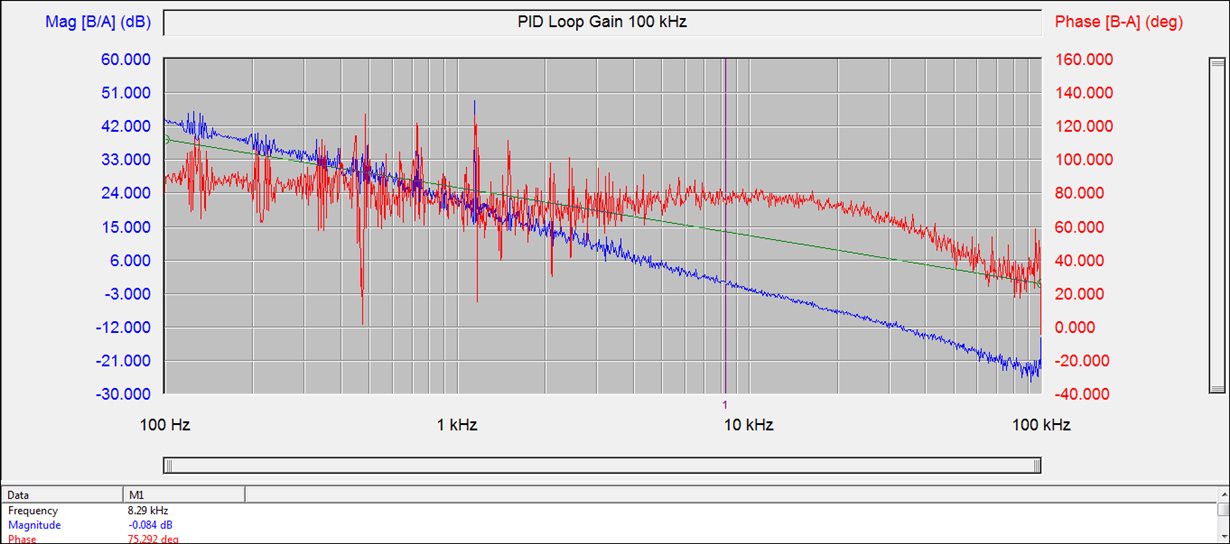

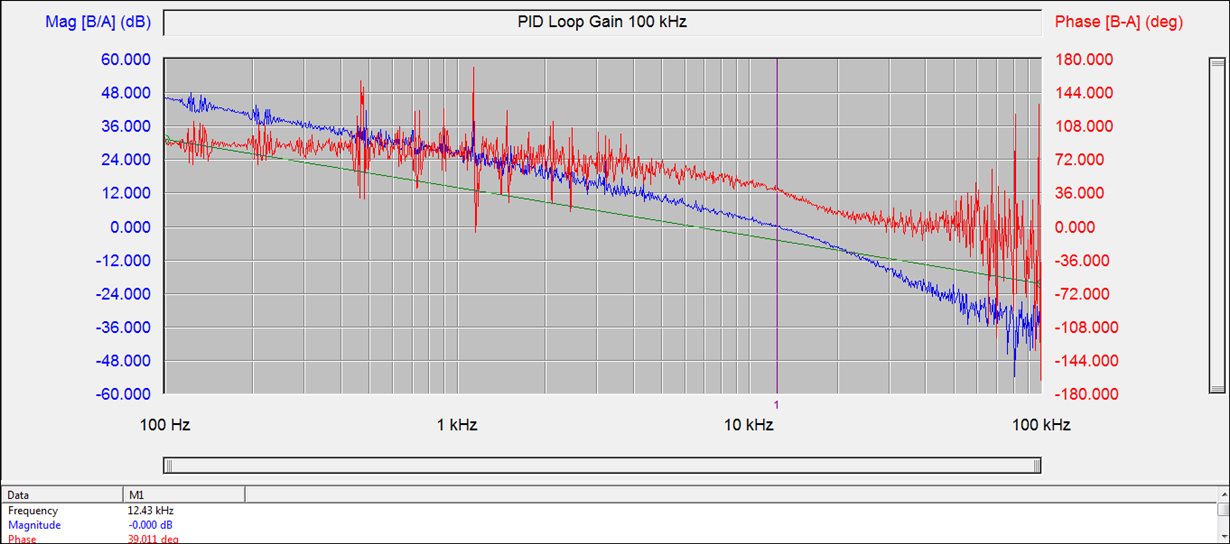

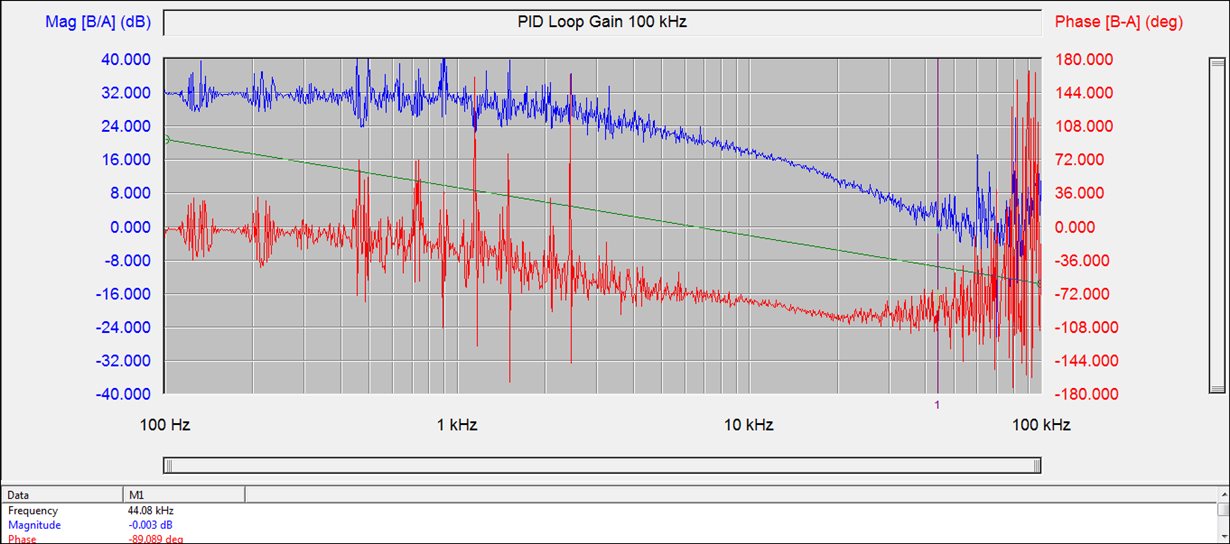

The solution to this was to lower the current sense resistance. In order to get a fairly smooth, monotonic startup, I had to reduce the current sense resistance to 2.5 mohm from its original 5 mohm. This caused some changes to the gain-phase response, so I also adjusted the control loop compensation. This is conservative but very stable:

Before there was some confusion about the phase margin - this is read directly, and is reported at the bottom: 75º at 8.3 kHz BW. This is with VIN = 13.8V and Iout = 3.0A. Above 3.5A the Bode plots are just noise.

I have ruled out power supply impedance interaction at the input, mainly because this instability actually gets better as VIN drops - the opposite of what you would see if the input impedance was causing problems. And I've ruled out low phase margin or gain margin in the control loop. I don't really want to lower the current sense resistance further because I'm worried about signal-to-noise ratio. What else could cause the sub-harmonic oscillation?

Thanks,

Chris