Other Parts Discussed in Thread: UCC27531

Hi Ti

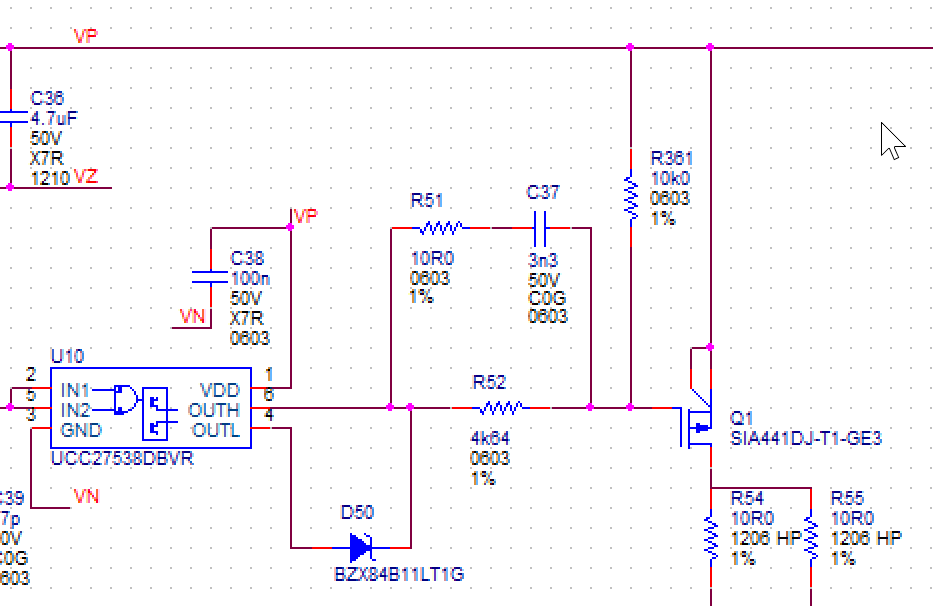

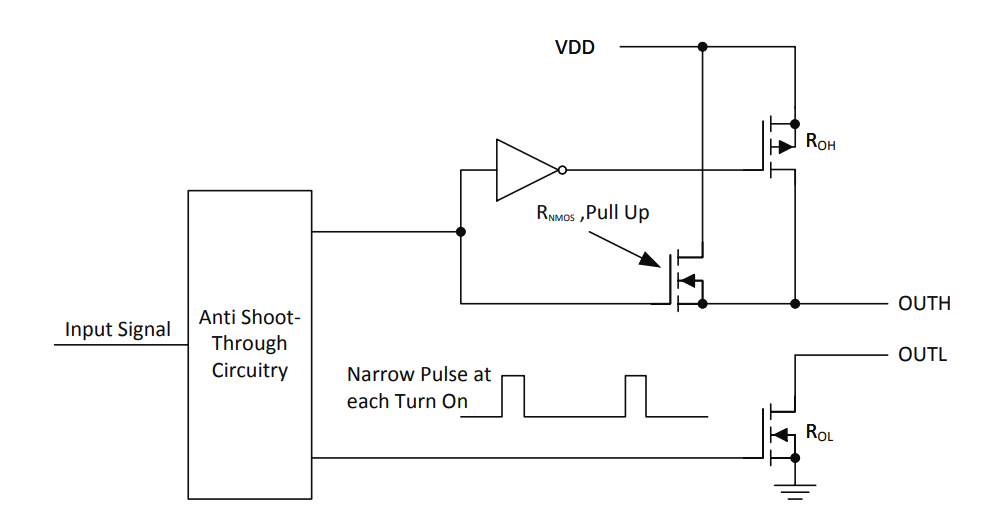

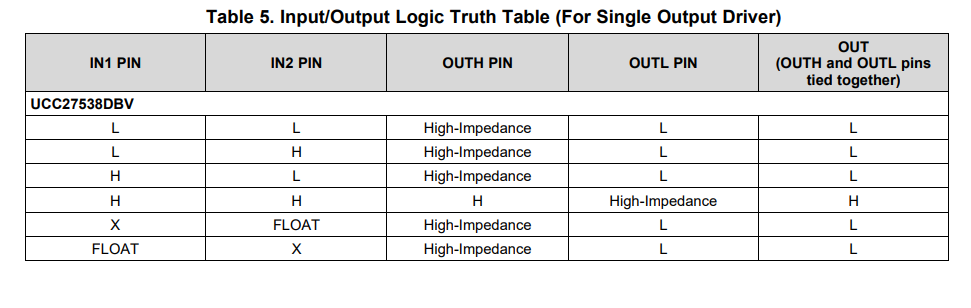

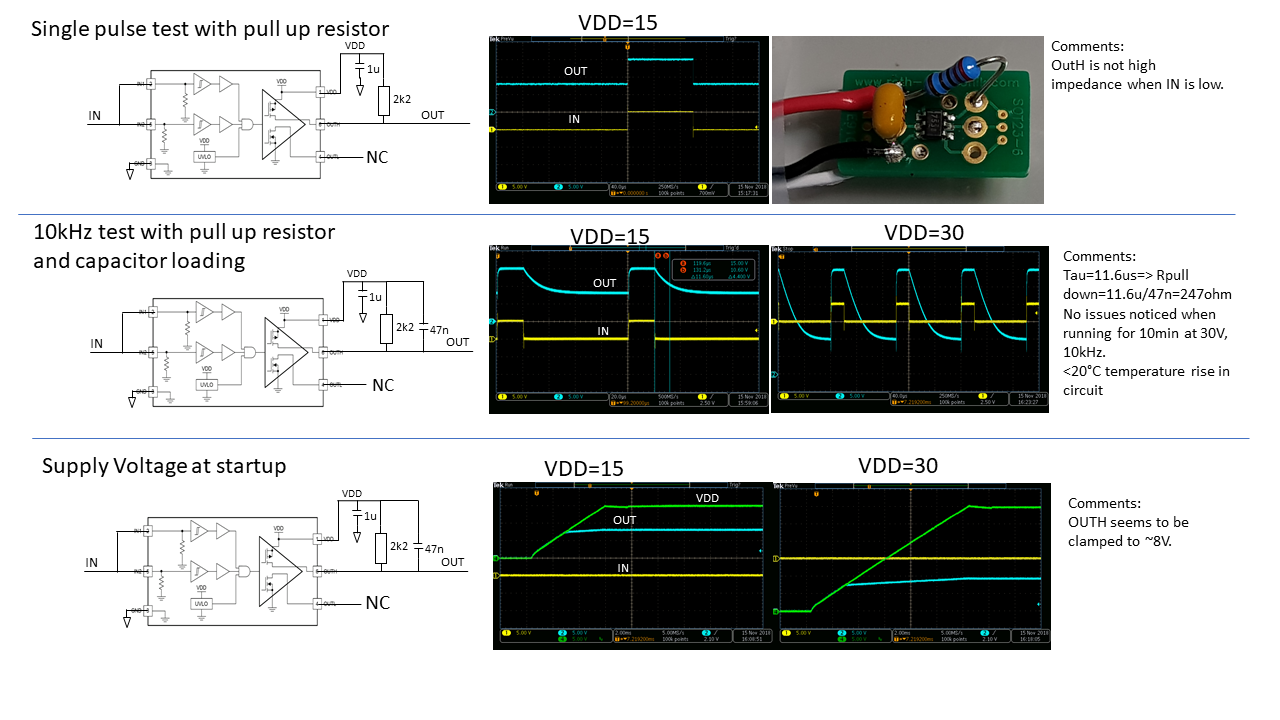

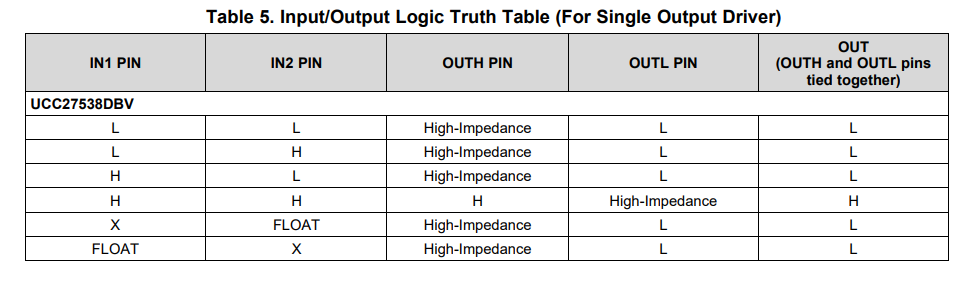

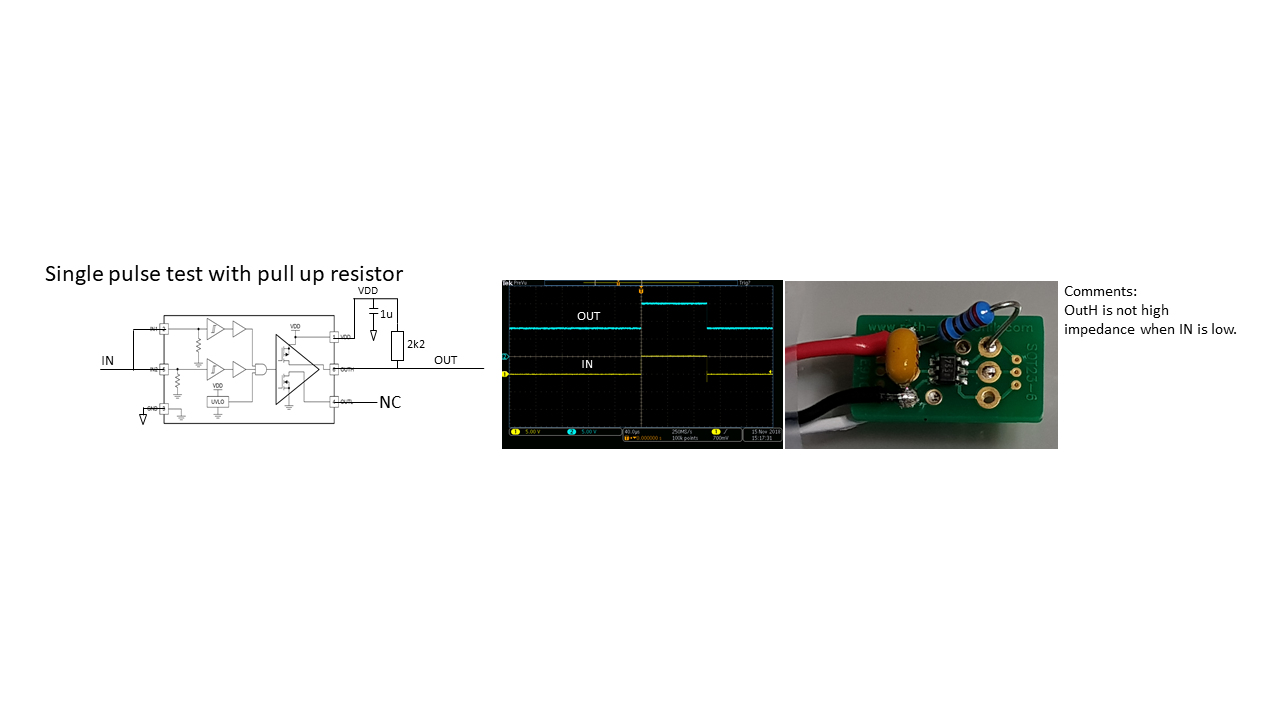

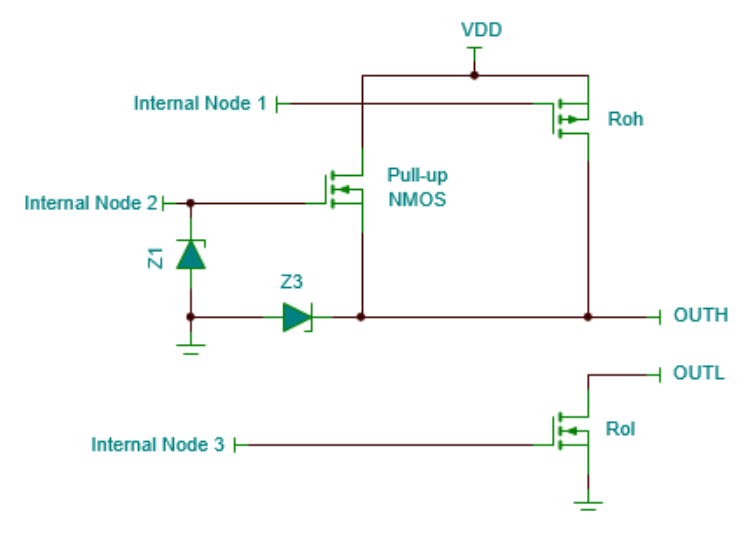

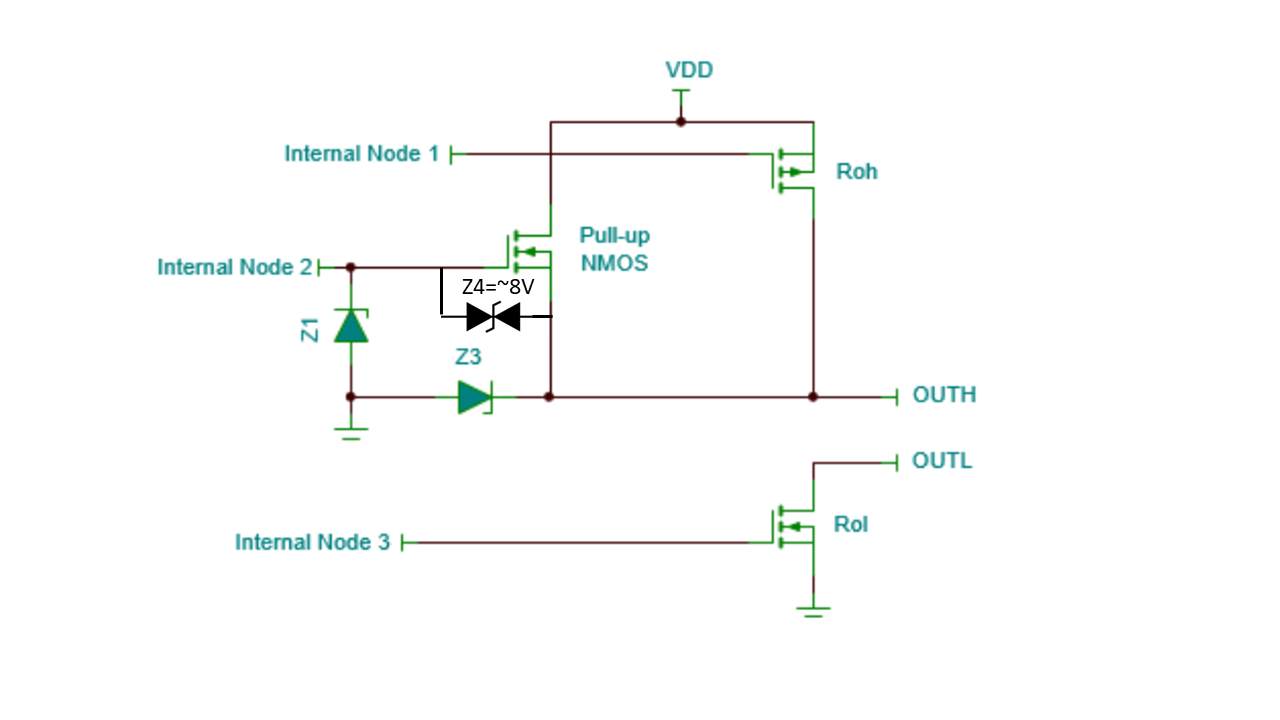

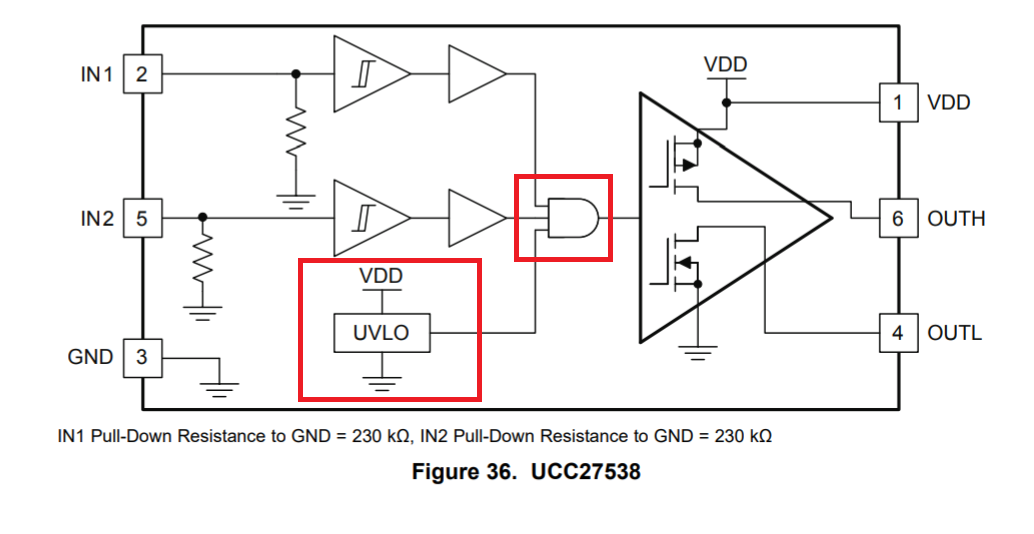

Is there some internal zener diode connected from OUTH to OUTL in UCC27538? (Similar to D50 in the schematic below)

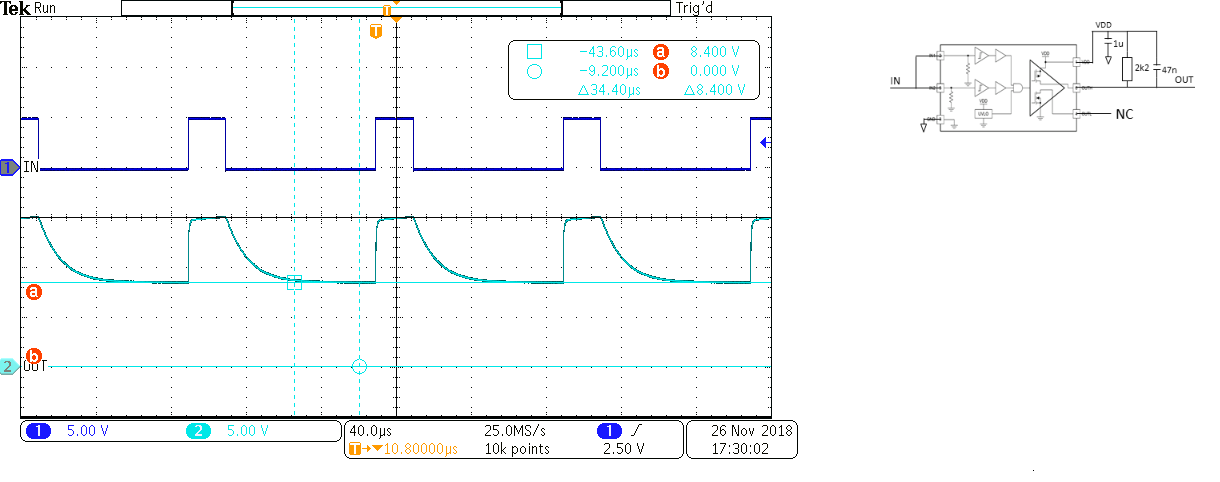

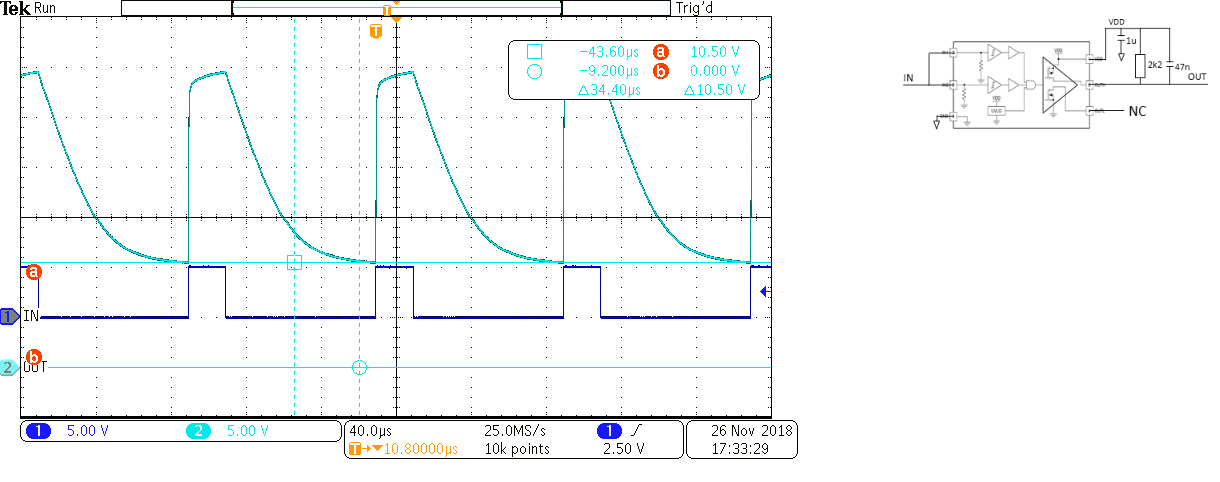

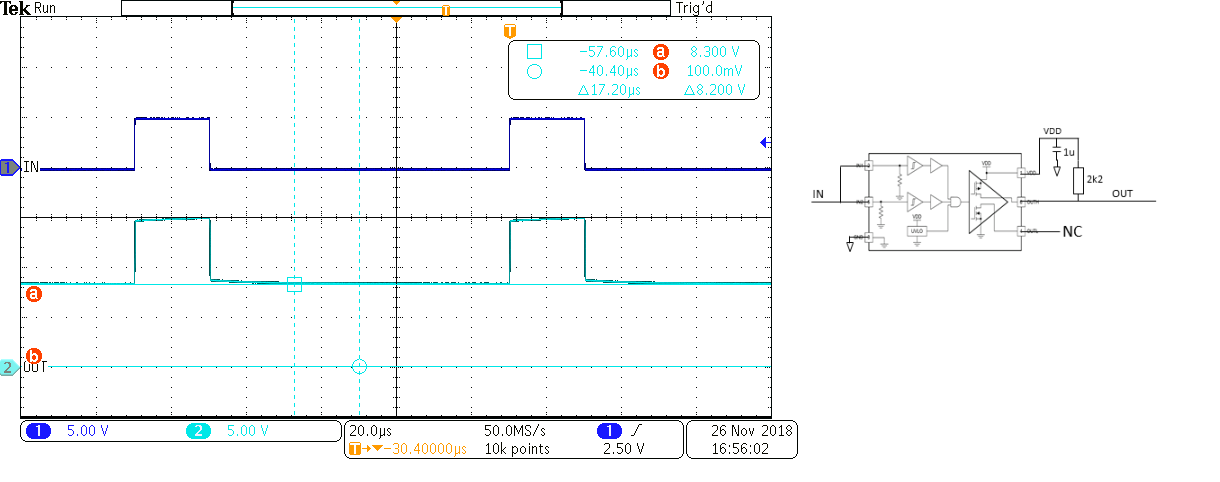

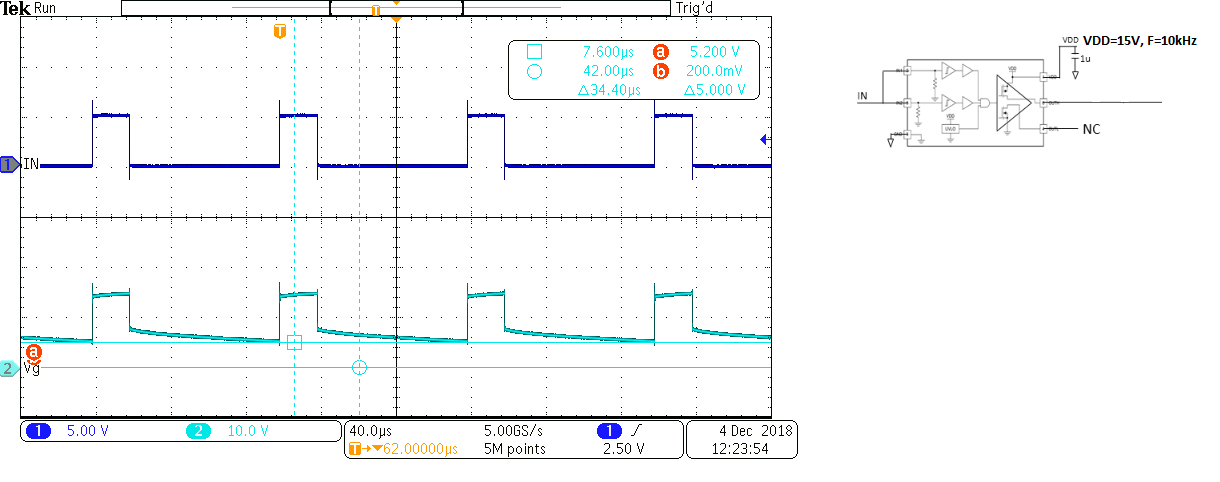

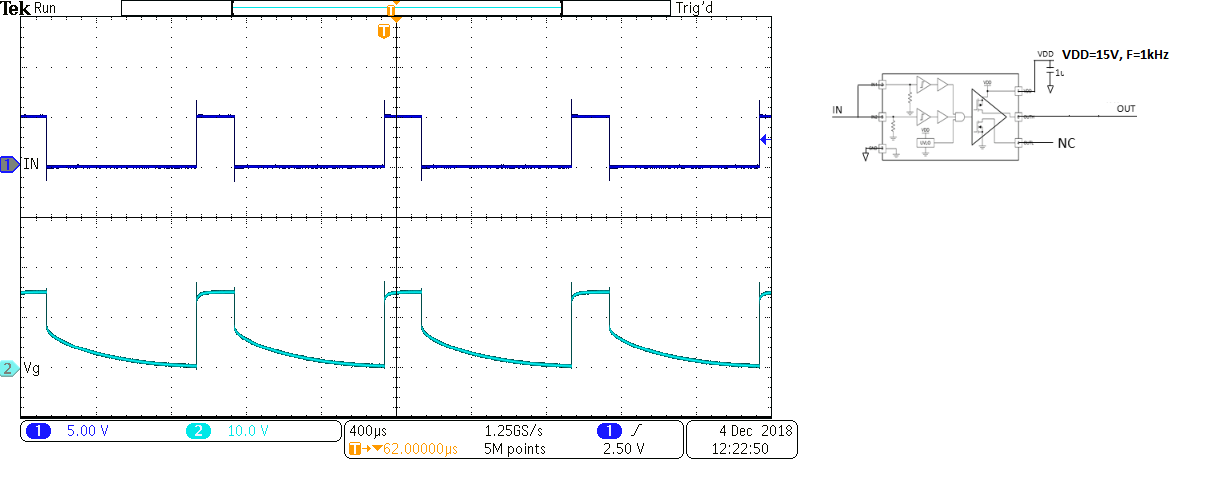

It seems to pull OUTH down to ~8V, when input goes low, even though OUTL is left unconnected. (In below schematic it happens even though D50 is disconnected)

Can I damage the device by using this zener? (I switch with very low frequency <200Hz, and only charge a few nF through 10ohm)

See schematic below: (VP=21V, VN=0V)

Regards,

Tune