Other Parts Discussed in Thread: ADS54J60,

Hi,

I'm using 4 TPS7A8300s for powering an ADS54J60 on a custom board. One of the requirements for the ADS54J60 is that you bring up IOVDD (1.15V) before you bring up DRVDD (1.9VD) or else the default register values won't be loaded correctly.

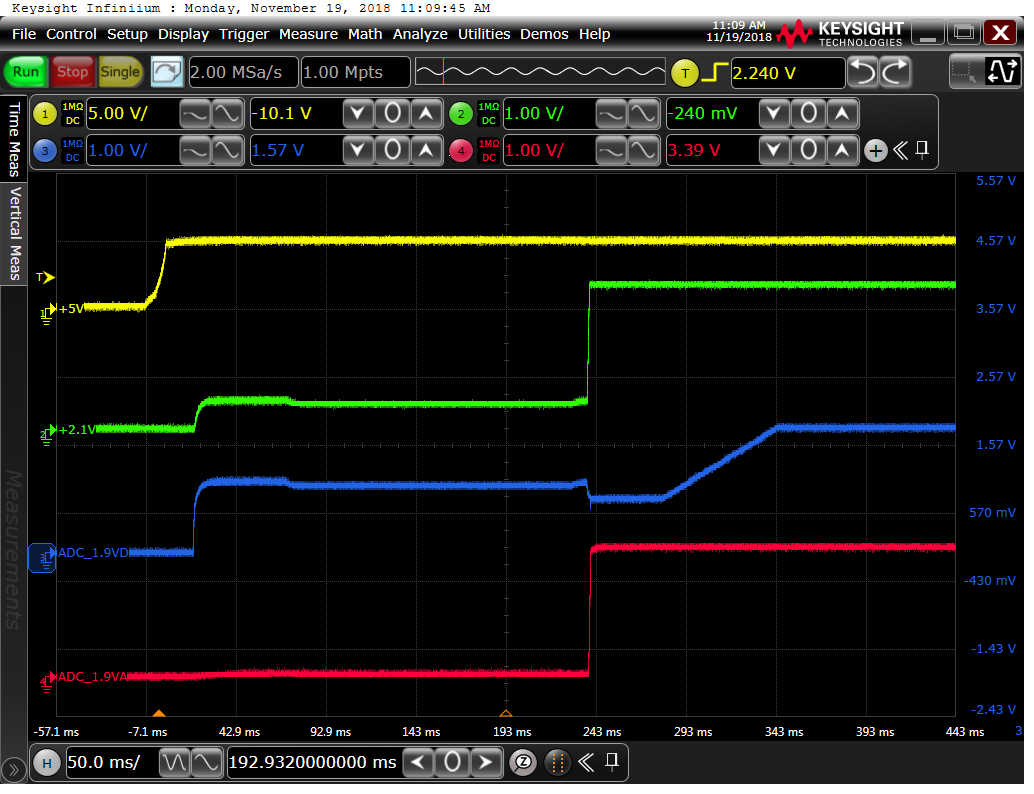

Below is a screenshot of the digital signals at the top of the screenshot in light blue, and they are driving the EN pins on each TPS7A8300 from an FPGA. The output voltages are measured at the bottom of the screenshot on Channels 1, 2, 3, & 4.

The FPGA comes out of reset (n_rst) and then sequences on the LDOs. The only problem is that the 1.9VD has about 800 mV present on the output even when it's supposed to be off.

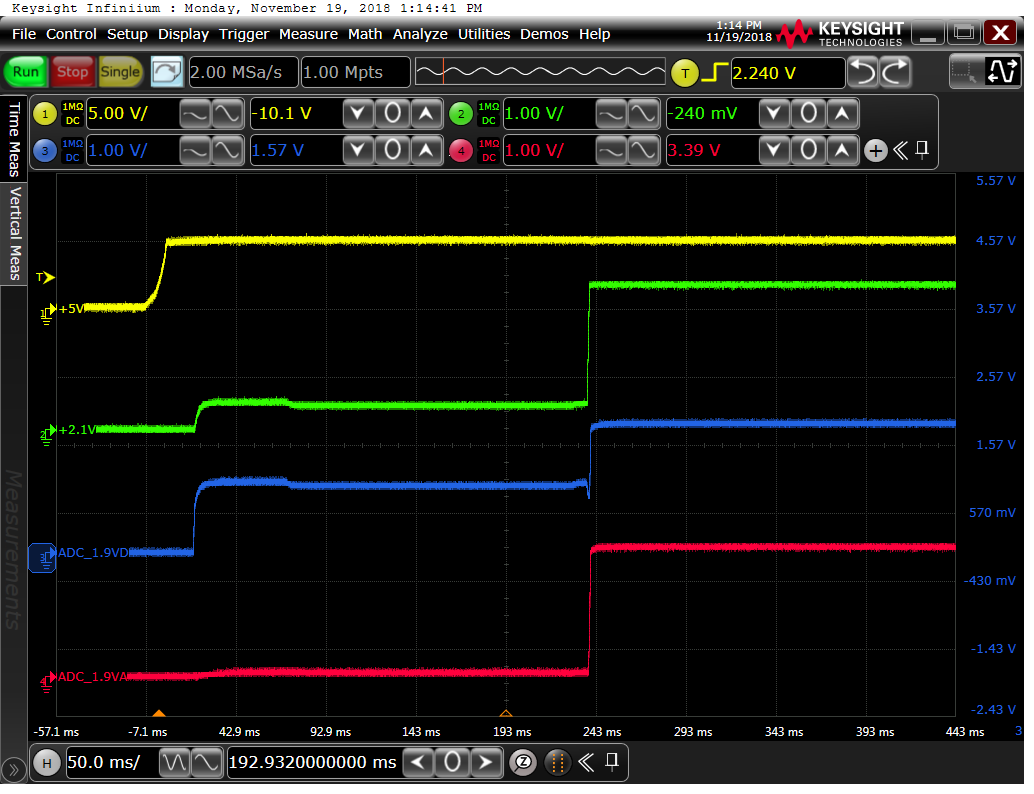

Zooming out, you can see that the 1.9VD rail comes up to 0.8V immediately on power-up, when every other rail is sitting at zero:

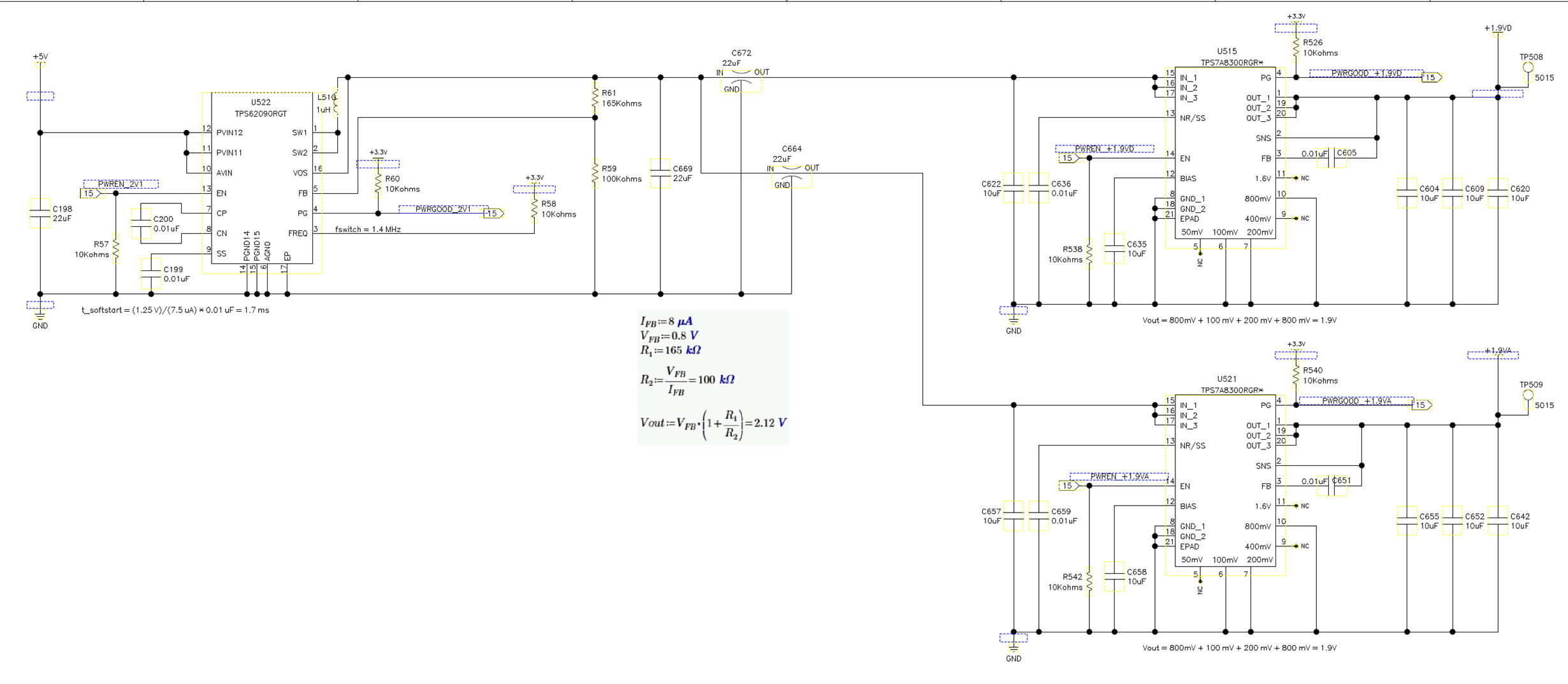

And my circuit for the 1.9VD: