Other Parts Discussed in Thread: UCD9246, , UCD74120

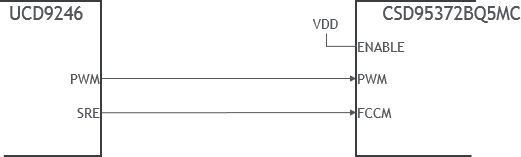

I need to interface the UCD9246 to the CSD95372BQ5MC.

I don't have the special 'E version of the UCD9246 that has the tri-state PWM function, and it likely isn't an option for this particular project at this time.

Instead, I need to interface the standard UCD9246 to CSD95372BQ5MC using the PWM and SRE outputs that are available.

The CSD95372B' has a tri-state PWM input, FCCM, and Enable pins.

Please suggest to best way to interconnect the digital outputs of the UCD9246 to the digital inputs of the CSD95372BQ5MC.

We do have an NDA with TI and have the full data sheets at this time.

Thanks, Best, Steve