Hello,

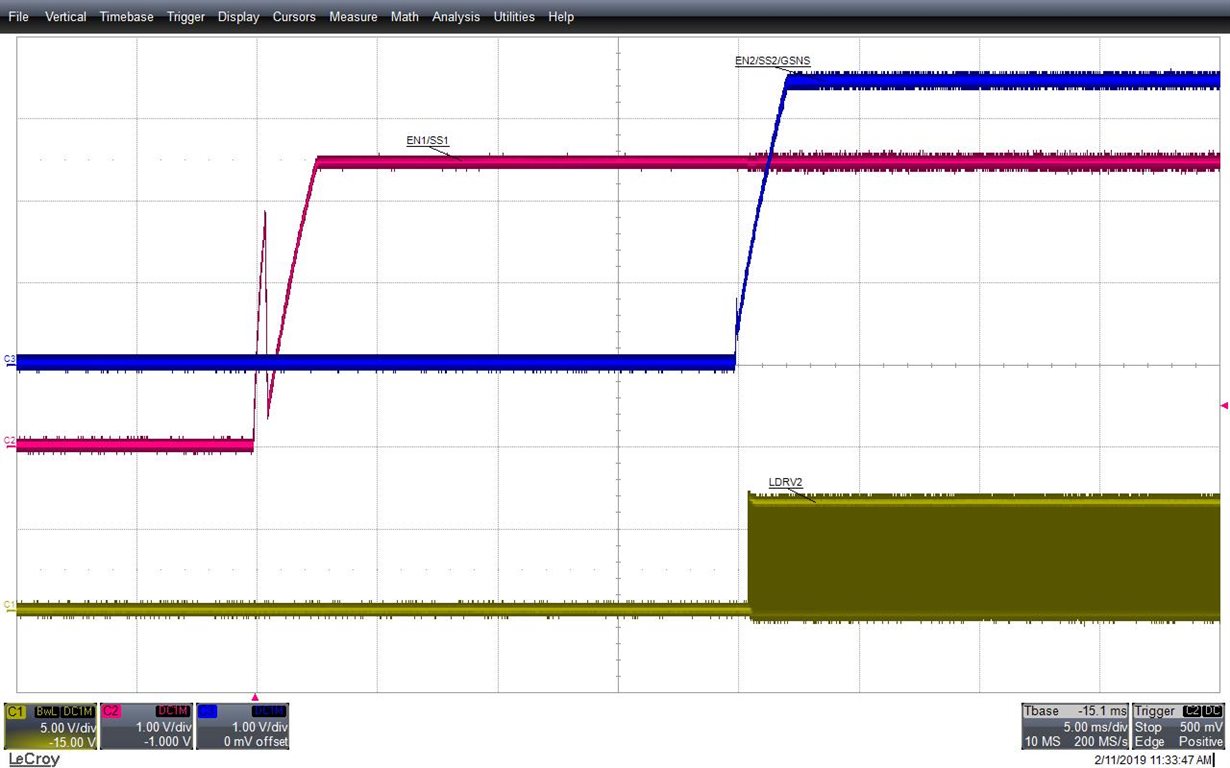

I use EN1/SS1 and EN2/SS2 separately on TPS40322 to sequence the power-up of my FPGA. I set 20 ms delay between each enable.

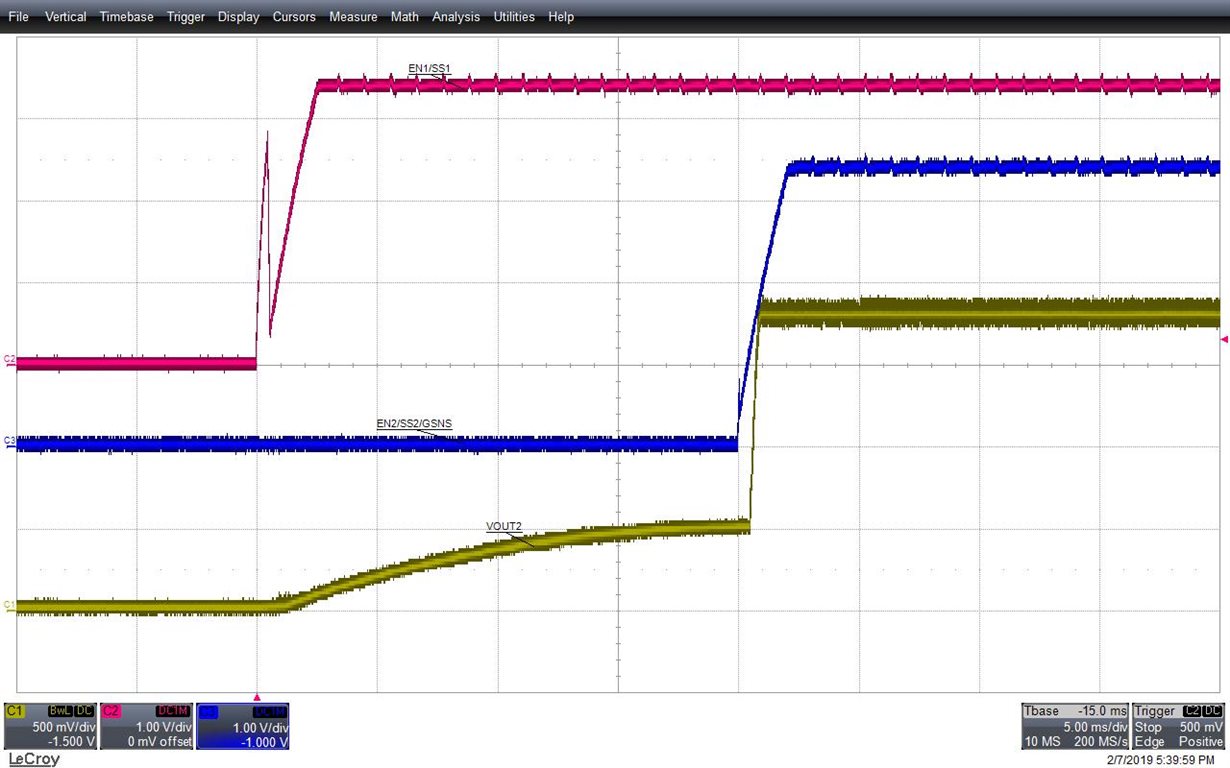

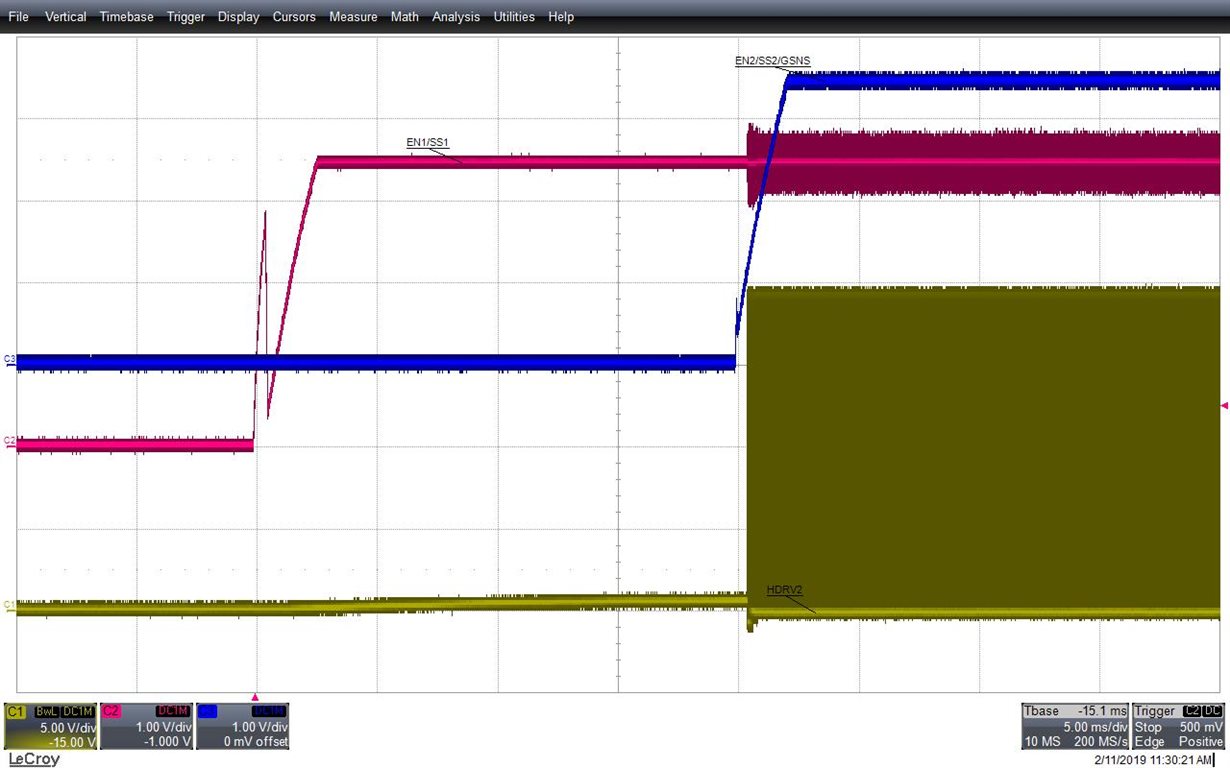

When I enable the CH1of the controller, VOUT1 (0.9 V) starts normally, but at the same time the VOUT2 voltage rise slowly about 0.5V and goes to 1.8 V when I enable the CH2.

My questions are:

Q1_ Is this behavior normal on CH2 or is something wrong in my design inducing this residual voltage? I would like no voltage on CH2 until I enable it (FPGA requirement).

Q2_ Why EN1/SS1 and EN2/SS2 don’t reach BP6 as observed in simulation ? (it seems to be clamped at half BP6)

Find attached my schematic and 3 waveform captures:

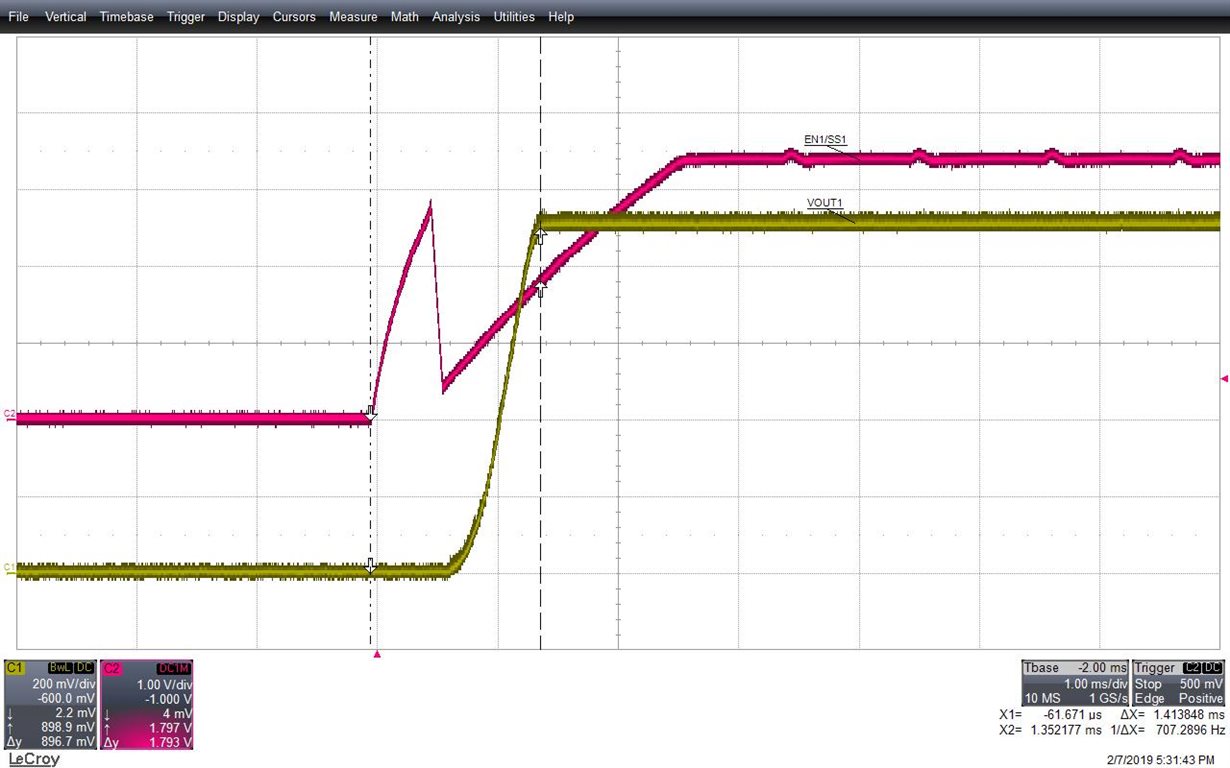

EN1&VOUT1

EN1&EN2&VOUT2

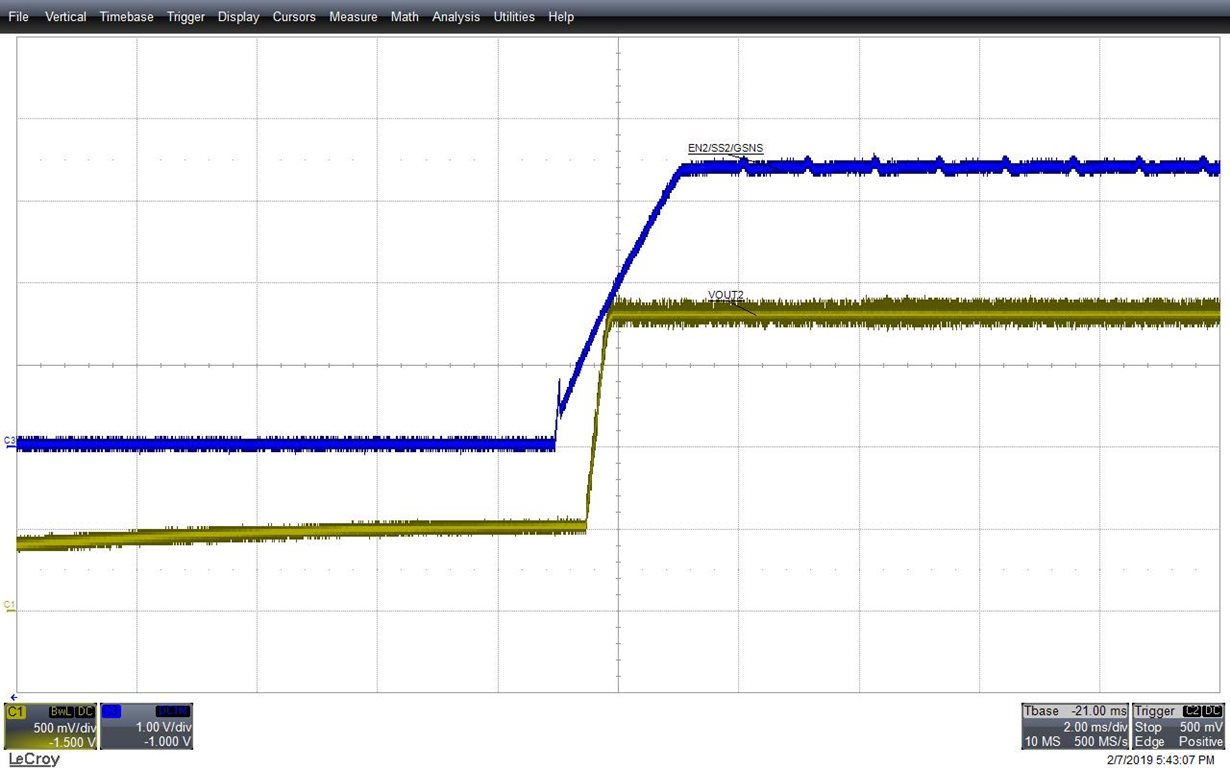

EN2&VOUT2

Regards,

PatrickTPS40322_Dual_Output.pdf