Hi,

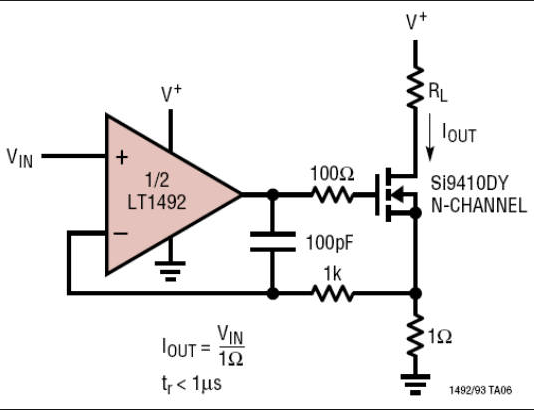

I've designed a circuit using the CSD18540Q5B as a constant current sink for a short time duration (4.5 Amps for 20mS) and successfully simulated in spice. The CSD18540Q5B is operated in the Saturation region and is controlled by a Op Amp (similar to the attached picture but with a much smaller sense resistor). I verified the MOSFET would not be damaged based on the power dissipation using calculations for junction temperature and derated SOA plot in datasheet based on case/ambient temperature. However, I was warned in a peer design review that some MOSFETS don't "like" to operate in the Saturation region and that planer gate MOSFETS works better in the saturation region but Trent or Super junction structures have areas of gate that can saturate and cause the MOSFET to blow up. Do I need to worry about the CSD18540Q5B having an issue with operating in the Saturation region as described above and blowing up based on the architecture of it's design?

Thanks, Nick