Other Parts Discussed in Thread: CSD18537NKCS, , UCC27282

Hi,

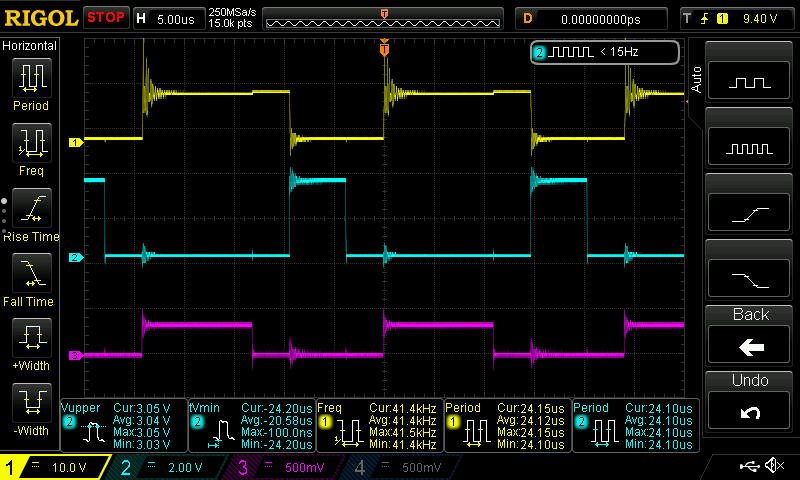

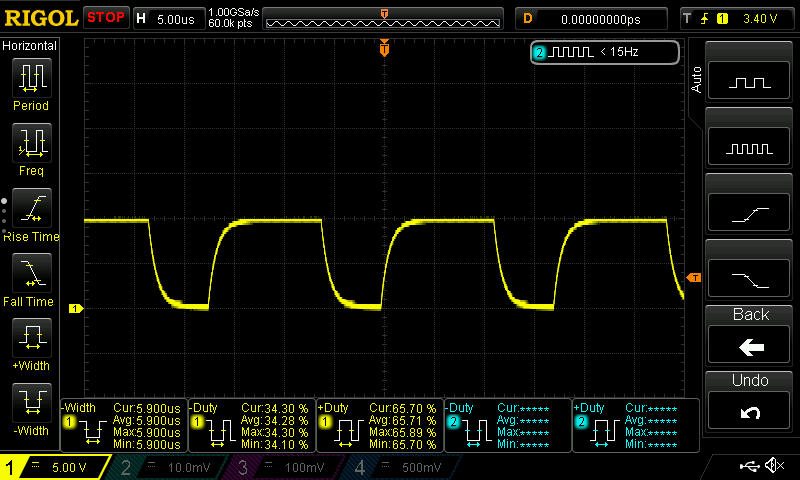

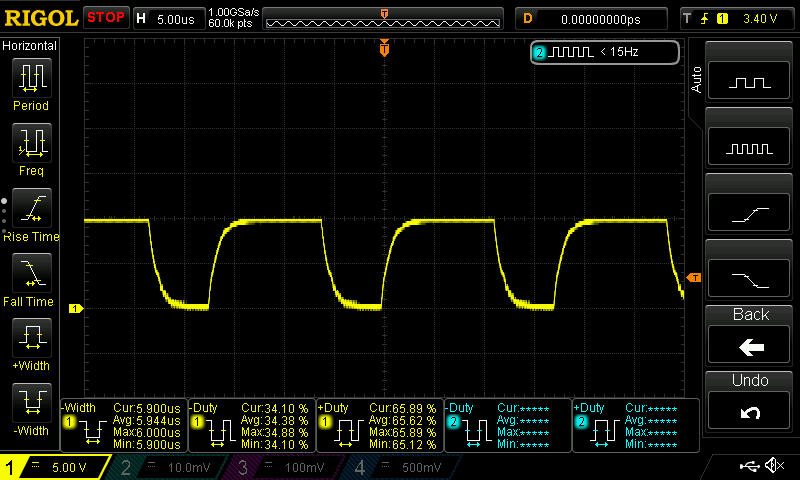

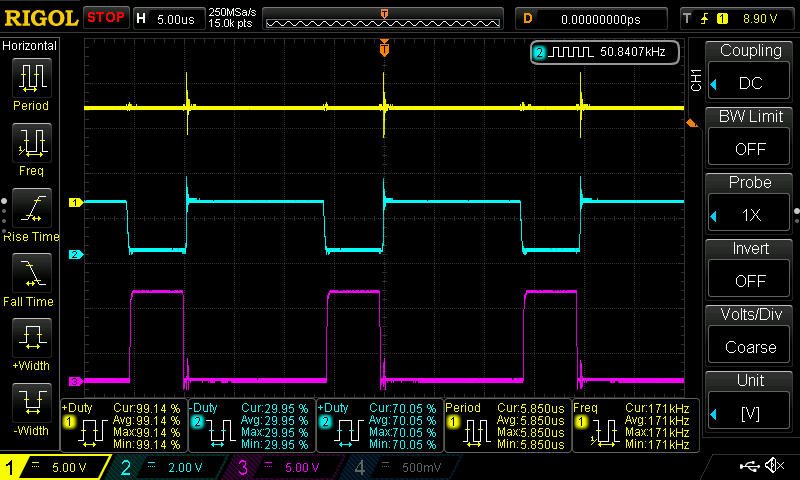

I'm using UCC27211A-Q1 to drive two N-channel MOSFETs (CSD18537NKCS) synchronously. I want to reduce the ripples for the switching waveform. Please find the attached screenshots of the switching waveforms and the PCB layout of the circuit. Do the ripples have to do anything with the dead-time between the two complementary PWMs supplied by controller to HI and LI pins of the UCC? How can I reduce the ripples for the switching waveform?