Dear, Sir.

My customer is designing their system applying TPS65263-1Q1.

Now, they are having several question relating the usage of Sync operation.

They will use 450kHz or 480kHz as the external Sync signal.

Please give your advice.

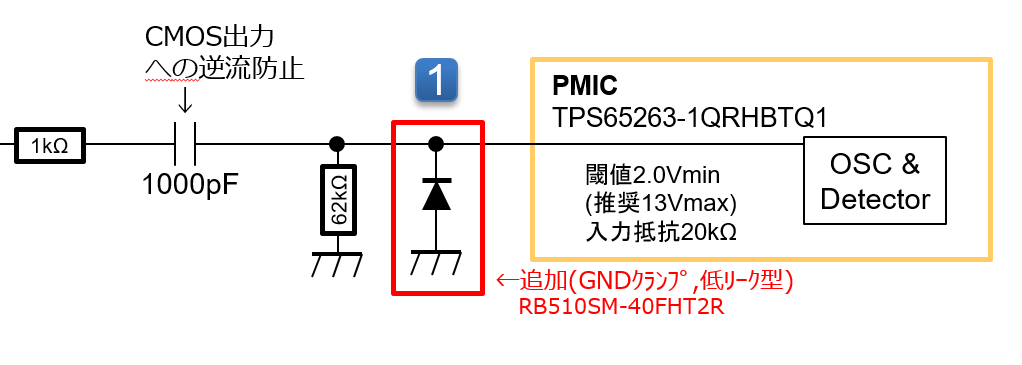

1. GND clamping diode & AC coupling capacitor.

They will put the diode for negative voltage clamp & the capacitor for

reverse flow avoidance. Is there any concern or side-effect?

2. The Sync signal is provided from OEM's front-end unit, not theirs

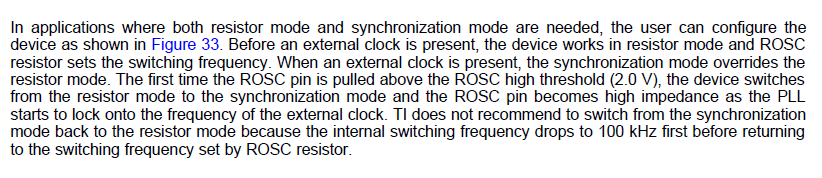

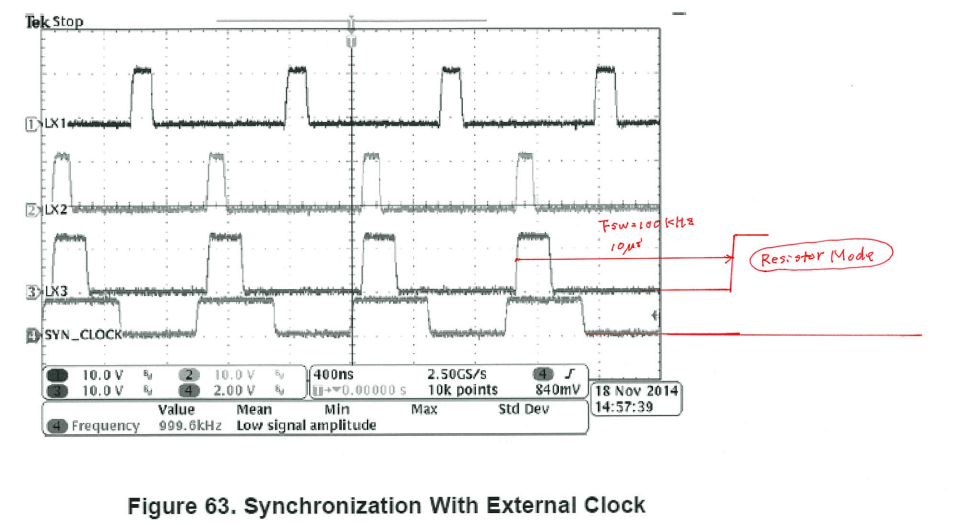

The comment is described on the datasheet not to recommend, but they

need to require OEM to maintain the proper Sync signal for eliminating fSW drop to 100kHz.

Sorry to ask this kind of matter, but hoping to get your advice at this time.

I guess fSW 100kHz operation would be un-lock to lock duration on the internal PLL.

If so,

1) Frequency deviation(amount of shift)_? Hz,

2) Duty change_? %,

3) Input signal amplitude_? V

4) No signal duration_? sec,

would be influenced for PLL enter to un-lock.

Please calrify those parameters if possile.

Best Regards,

H. Sakai