Hi Team:

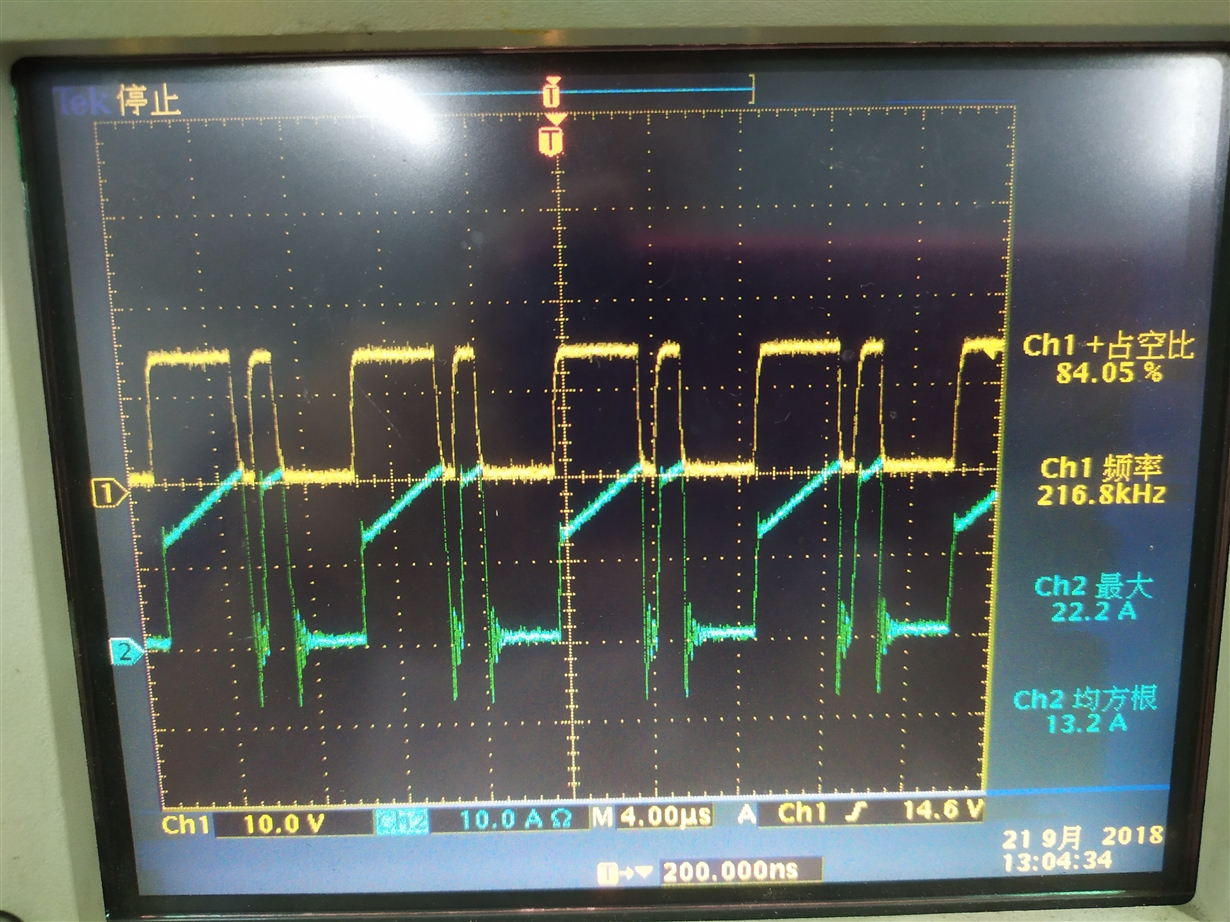

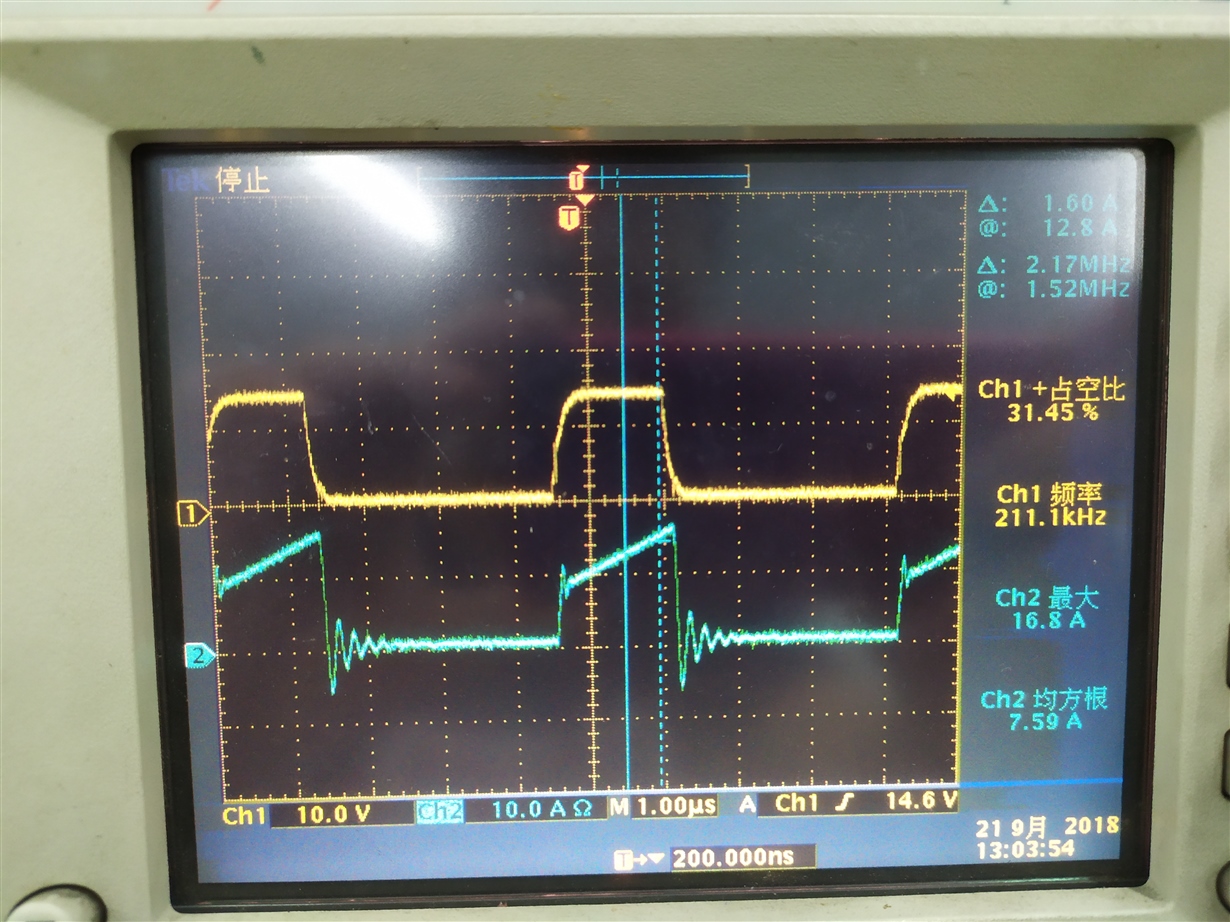

RD feedback when Vin_min Vgs waveform anomaly and Vin_max is normal as attached.

Pls help to confirm ~ what's issue may cause Vgs waveform anomaly ? (setup issue ? layout issue?)

Condition:

Vin_min=13V , Vin_max=24V

Vout=12V , Iout=6A

turns ratio=3:6

Lp=800nH

Rg=10 ohm

Could you share layout guidelines for reference ?

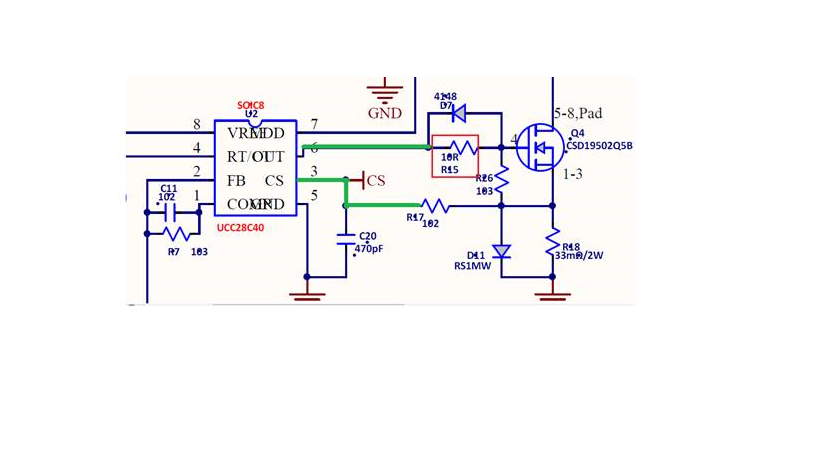

As I check , RD use double layer PCB and two trace parallel of OUT & CS as green line as below

will it cause Vgs anomaly ?

thanks.

Regards / Mark