Other Parts Discussed in Thread: TPS40303

Hi TI Expert,

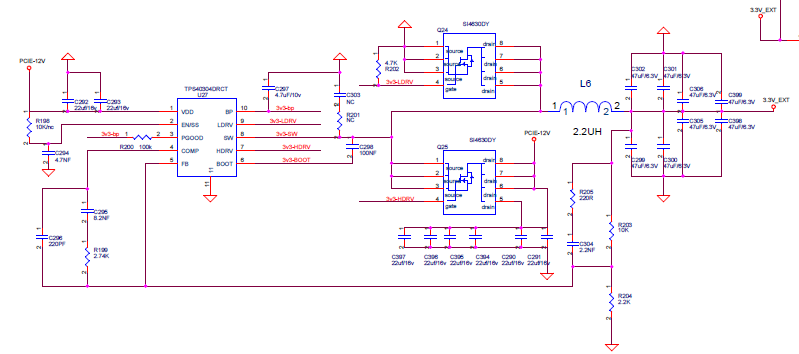

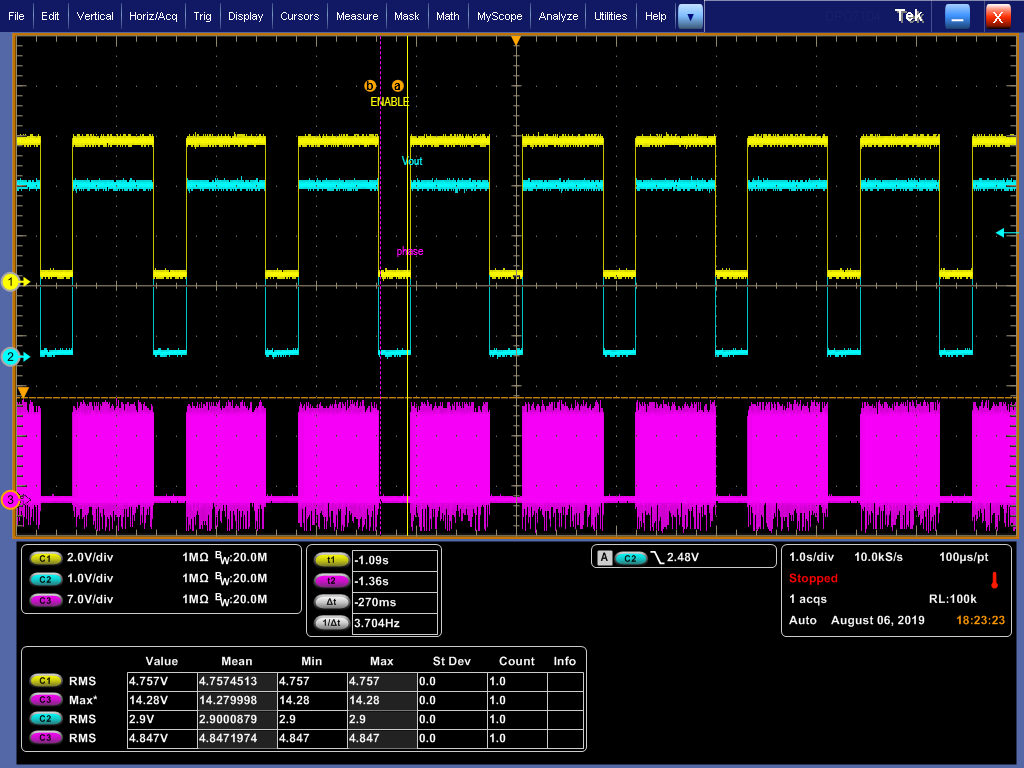

We are using TPS40304 for a 12V to 3.3V DC/DC design. The 3.3V shuts down in high temperature(73deg.C ambient). TPS40304 could be 90degC or higher.

We suspect it triggers OCP in high temperature. And seems our issue is similar as the issue mentioned in below link. Could you share the detail reason behind this issue? Seems the issue is resolved by adding a 4.7ohm resistor in series with Boot CAP.

We will have a try. About over current of highside MOSFET, what's sensing point of Highside MOSFET Rdson, is it sensing the voltage difference between VDD and SW?

http://e2e.ti.com/support/power-management/f/196/p/657197/2415089#2415089?jktype=e2e

Thanks,

Dora