I have a problem with a boost converter based on the LM5122 and hope somebody could help me finding the cause.

The hiccup overload protection operates when the load becomes higher than ~600mA.

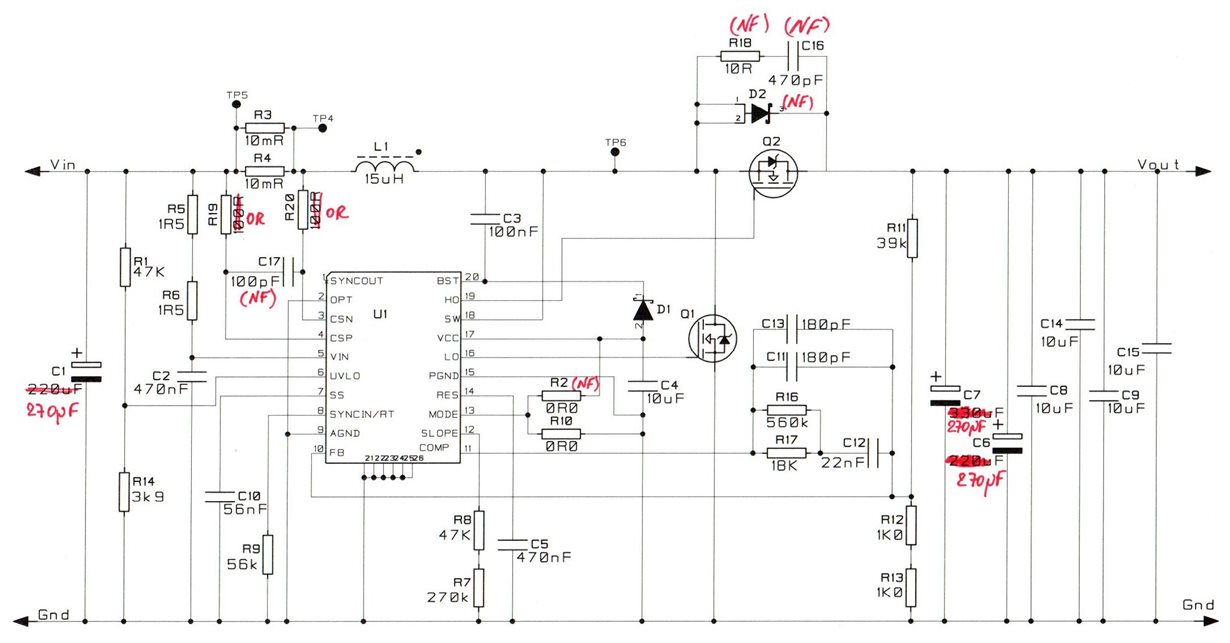

Design made using Webench

Vin [18V - 22V]

Vout 24V 8A

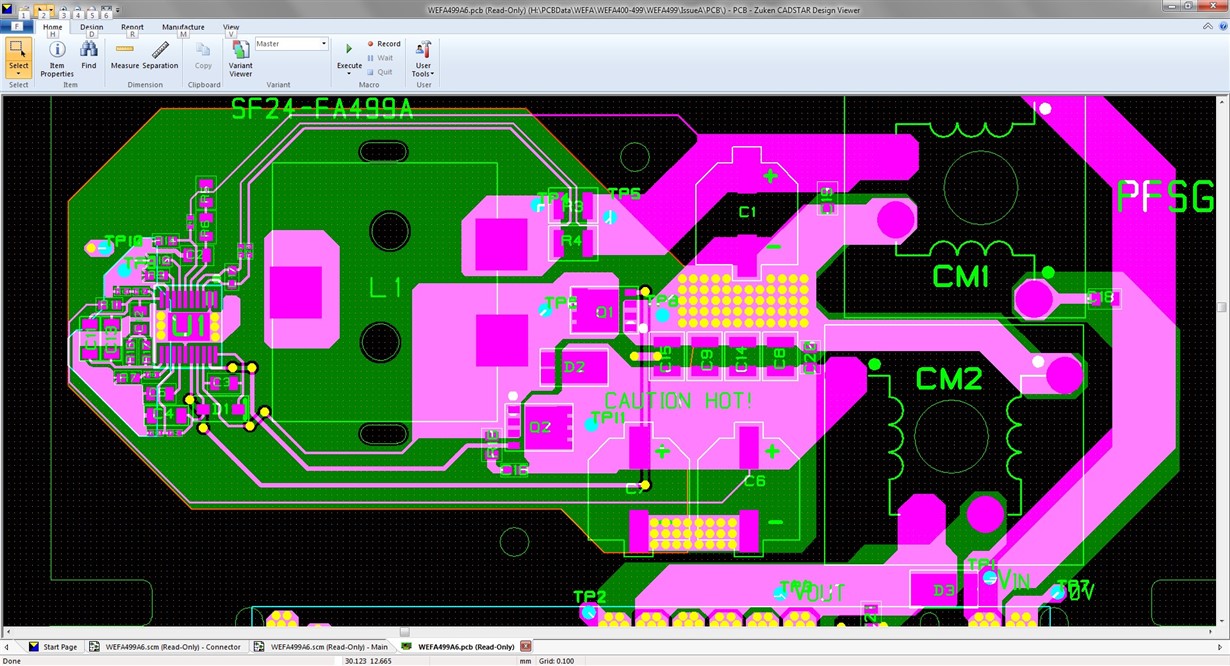

see below schematic, the layout has been made based on the LM5122EVM-1PH

Q1 CSD18503Q5, Q2 CSD18509Q5BT

What I have noticed

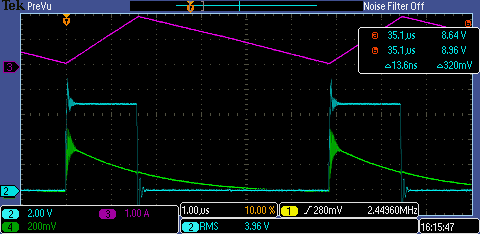

1) the problem seems to happen when the high side FET starts being driven.

2) pulses are generated on the RES PIN when the low side FET is turned ON

Below are scopes captures made with a ~700mA load (C5 replaced by a 27k on RES PIN to see when the limit operate)

CH2 gate of Q1,CH3 current in L1, CH4 RES PIN