Hello

My customer is evaluating TPS7A78EVM now. They have a question.

Could you please support the following question?

Customer comment is below,

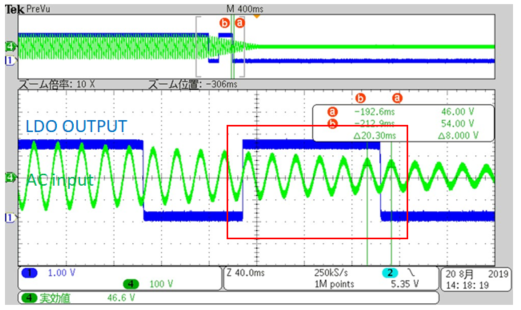

We do a slow-down test on TPS7A78EVM (Half-bridge mode) and can't understand a waveform under slow-down mode.

So we need an explanation from IC designer.

Test condition

Slow down conditon: 100V/0.5s

Start voltage: AC100V

loading conditions: 390Ω

What we are concerned about is why the LDO output voltage can be recovered under slow-down mode?

Thanks

Muk