Other Parts Discussed in Thread: UCC21732

Hello TI Team,

We have a new project for passenger vehicle motor drive, where we tried to simplify our existing gate driver design using UCC21732. We built board and are using it on FF600R12ME4C module (half bridge) just for testing.

Three boards combined spins the motor just fine for now (not fully tested) except for occasional UVLO and desat trips.

We narrowed down problem where we can reliably reproduce it. SCH below:

PS voltage is +16V, -4.7V. On the PWM input is Rigol DG1022 signal generator. We can switch HS or LS or both IGBTs, same problem.

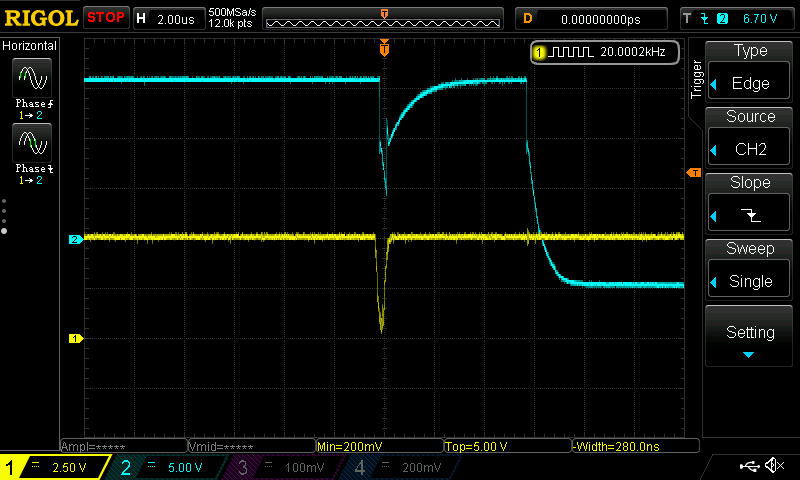

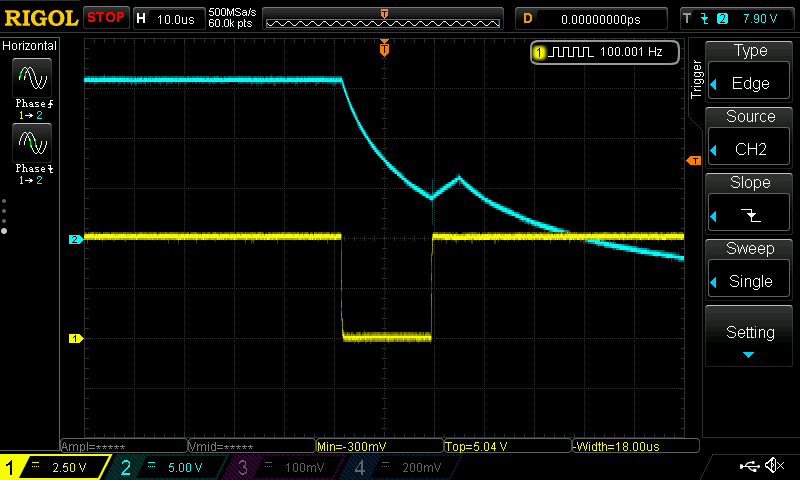

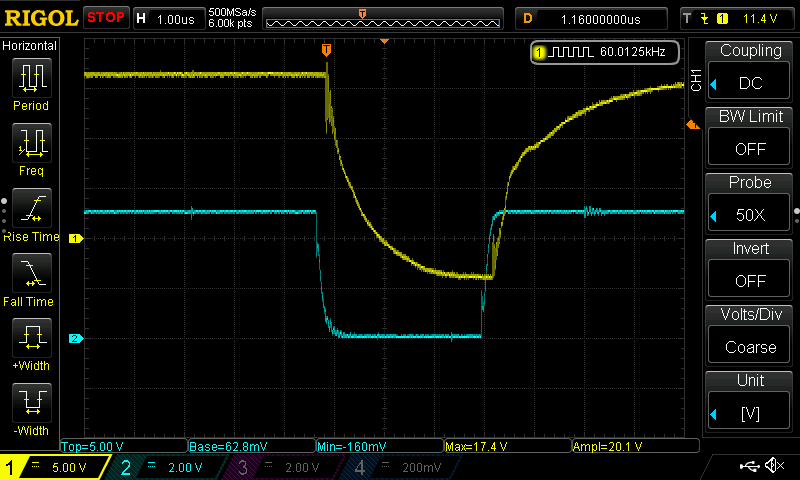

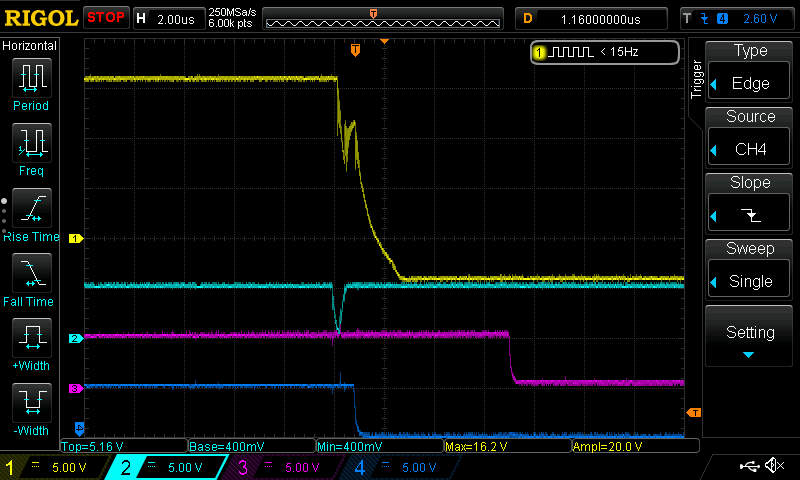

Scope screenshot:

CH1 yellow: PWM input

CH2 blue: IGBT Gate (differential probe between E and G)

With narrow pulse, approx. 300ns wide, UVLO fault happens. IGBT is turned off after 5us just like datasheet says (VDD UVLO off delay to output low). IGBT turns back on after 0.8ms, as per DS.

If we decrease pulse width even further we get desat fault. UVLO and desat faults happens only with high duty cycles (>99.4% @20kHz). We could not reproduce problem with low duty cycles (when signal goes high for short time).

Short circuit between E and C to bypass desat - no change. Short circuit between pins 2-3 - no change.

PWM frequency also doesn't matter, only pulse width.

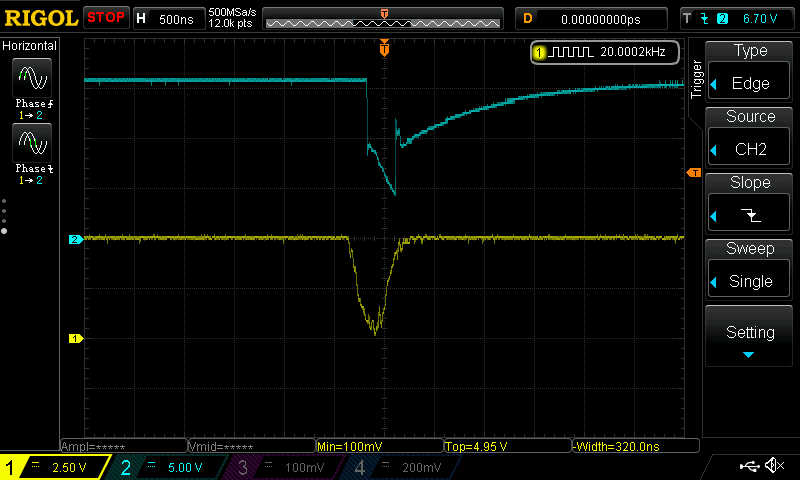

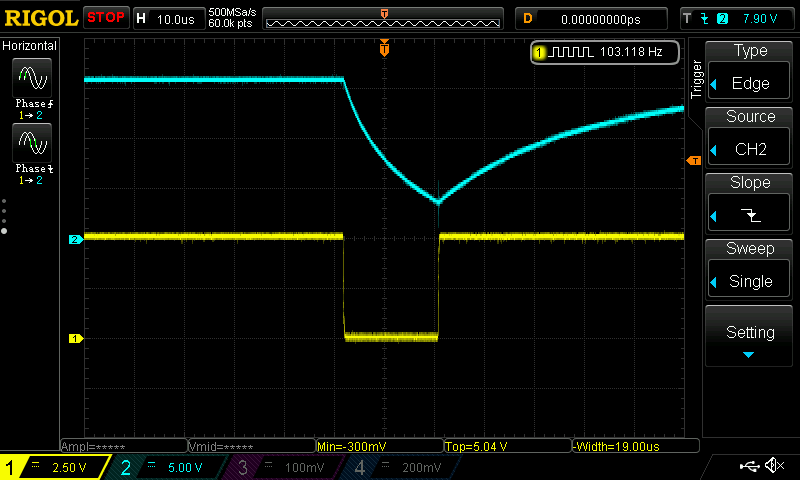

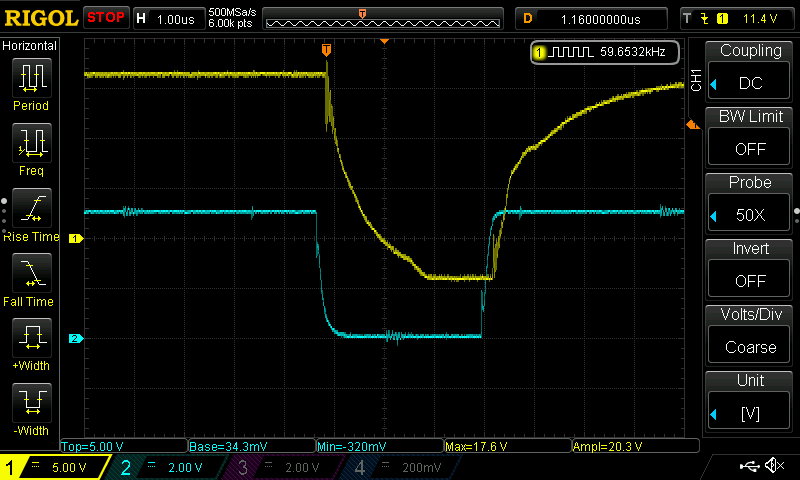

Zoomed in pic:

CH1 yellow: PWM input

CH2 blue: IGBT Gate

It looks like it happens when IGBT doesn't have enough time to fully turn off. Gate voltage manages to go down only to 4V.

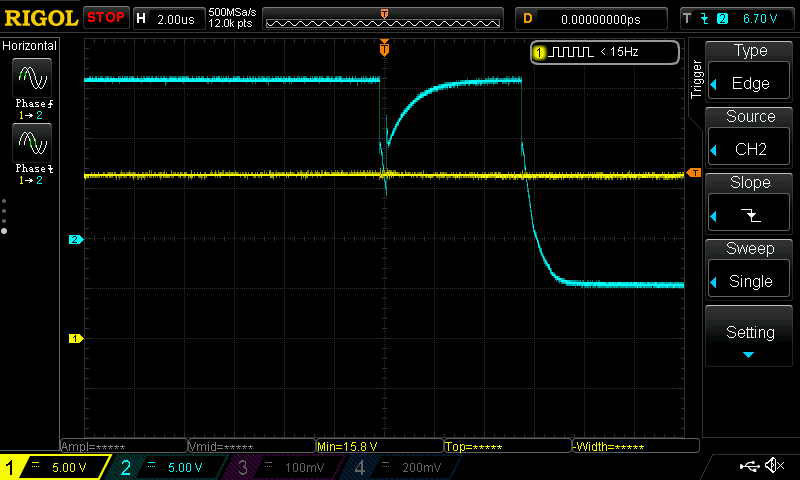

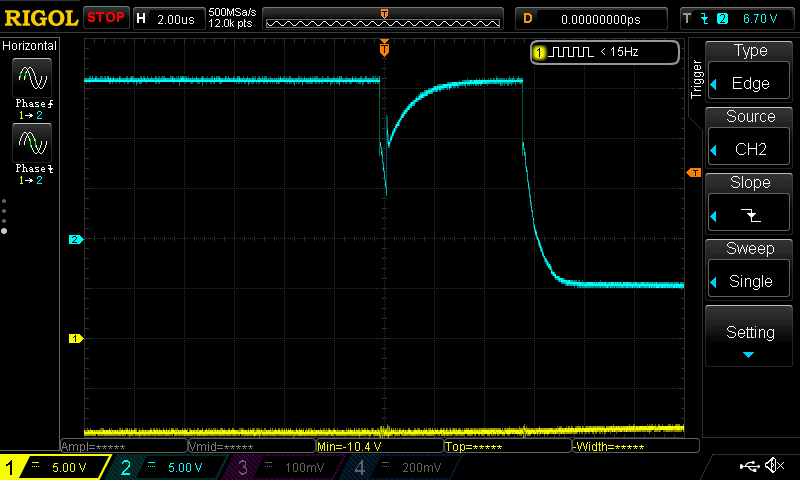

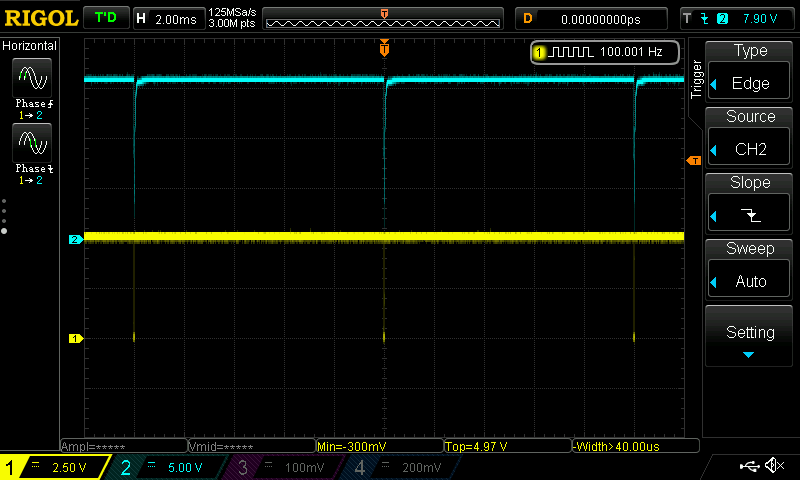

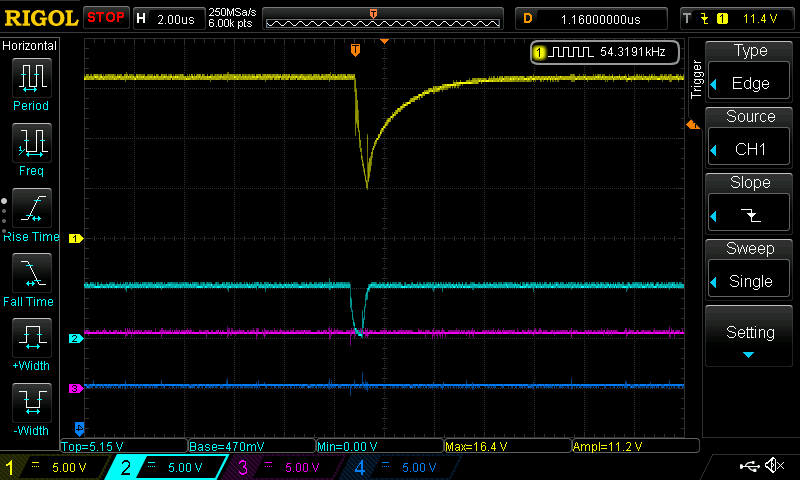

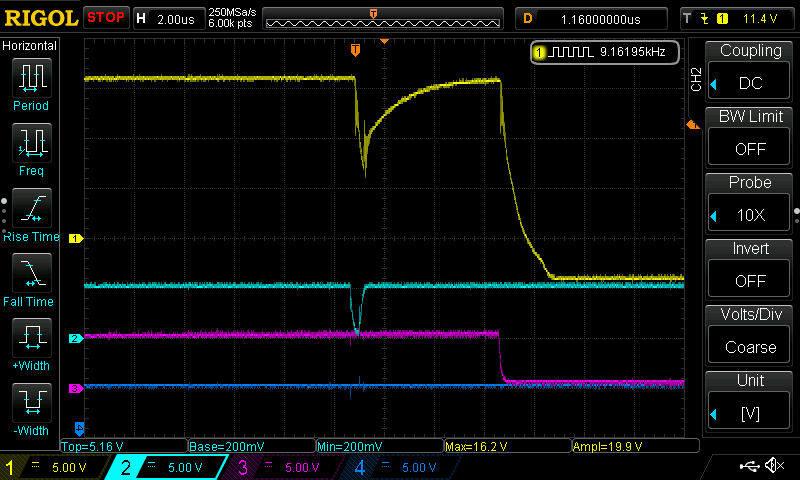

PS voltages two pics below:

CH1 yellow: Voltage between driver pins 3 and 5 (COM and VDD)

CH2 blue: IGBT Gate

CH1 yellow: Voltage between driver pins 3 and 8 (COM and VEE)

CH2 blue: IGBT Gate

PS voltages looks stable enough with sufficient margin to not trip UVLO levels.

We could reproduce the same problem with 10nF foil cap on gate, instead of IGBT, with pulses less than 200ns, so some of my colleagues expressed worries that noise on short pulses could be source of the issues.

So we removed IGBT and put 10uF cap on the gate. This should be slow enough to eliminate short pulses theory. We needed to modify PS (put a LOT of caps) for this to work. PWM frequency is set to 100Hz. Desat sense is shorted.

Normal operation (PWM pulse width >18us):

CH1 yellow: PWM input

CH2 blue: 10uF Cap (diff probe close to gate resistors)

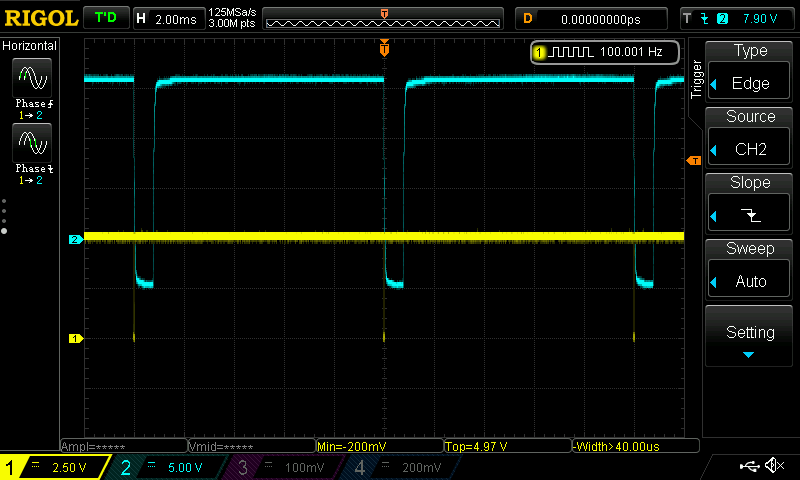

Fault (PWM pulse width <= 18us):

CH1 yellow: PWM input

CH2 blue: 10uF Cap

UVLO fault triggers when gate voltage could not fall below 4V. If we decrease pulse width even further desat fault latches output to -4.7V.

We can provide more details if needed, please advise.

Kind regards,

Zoran Halić