Other Parts Discussed in Thread: TL431, UCC28720, UCC28600, LM5023

Hi,

I am having problems with a AC.DC convertor based on UCC28740 5V/3A

My VS is under 4V , CS at around 800mV and switching frequency (1A) around 30Khz

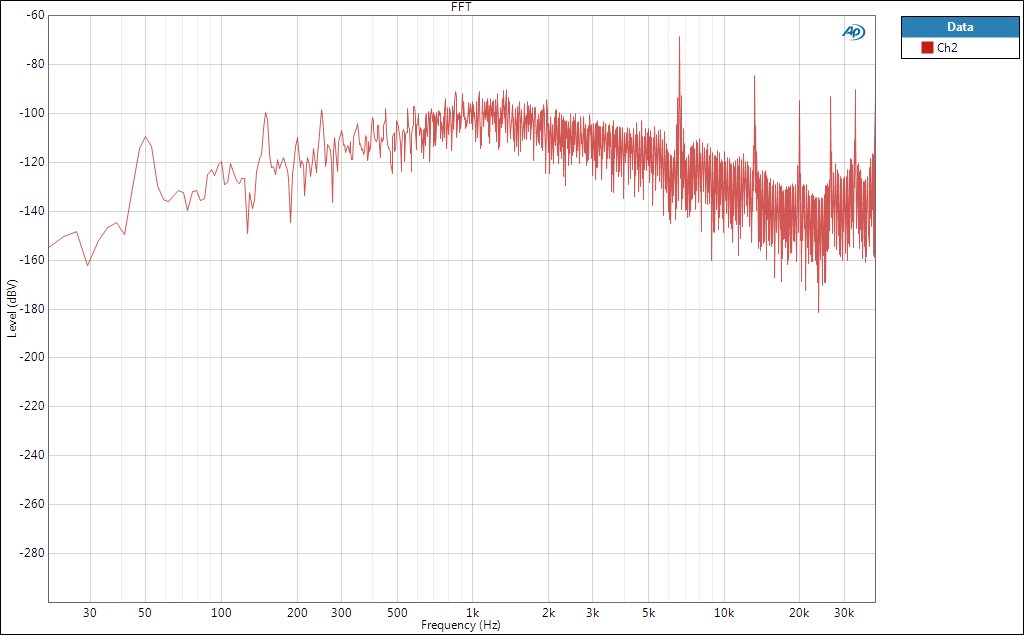

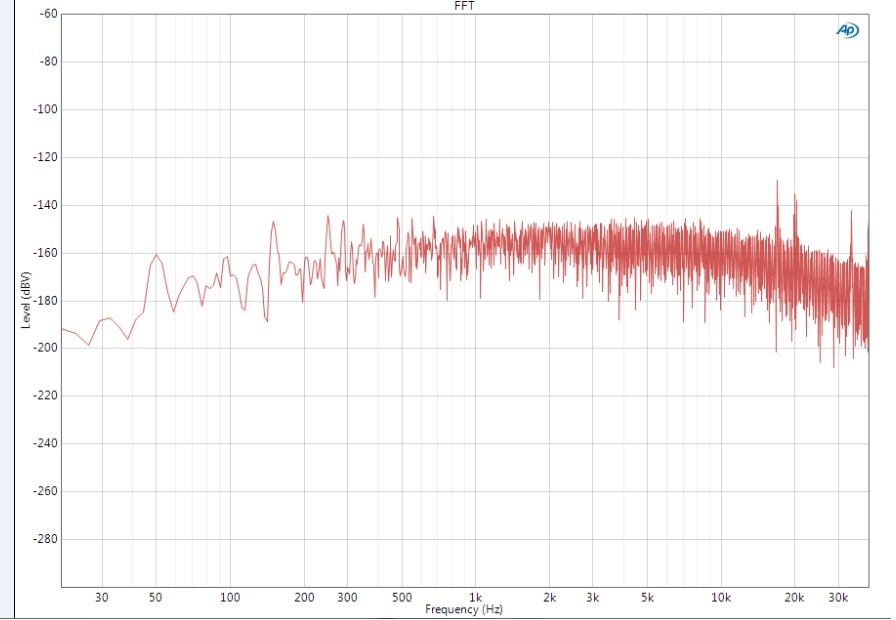

What I observe is that every 2ms mosfet stops working. So for 2ms (around) its switching normally at 30Khz , then 2ms it stops completely , then again in starts. Because of this behaviour , we get noise.

What can explain this behavior ?