Hi, Ti power management experts,

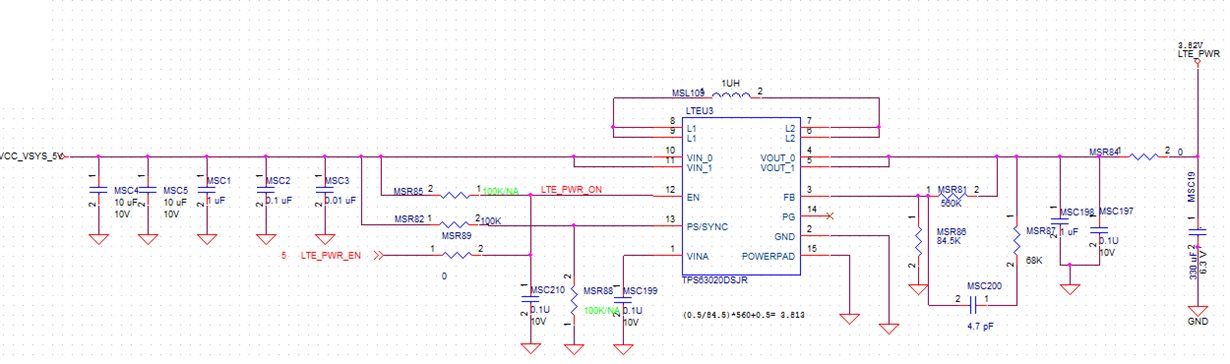

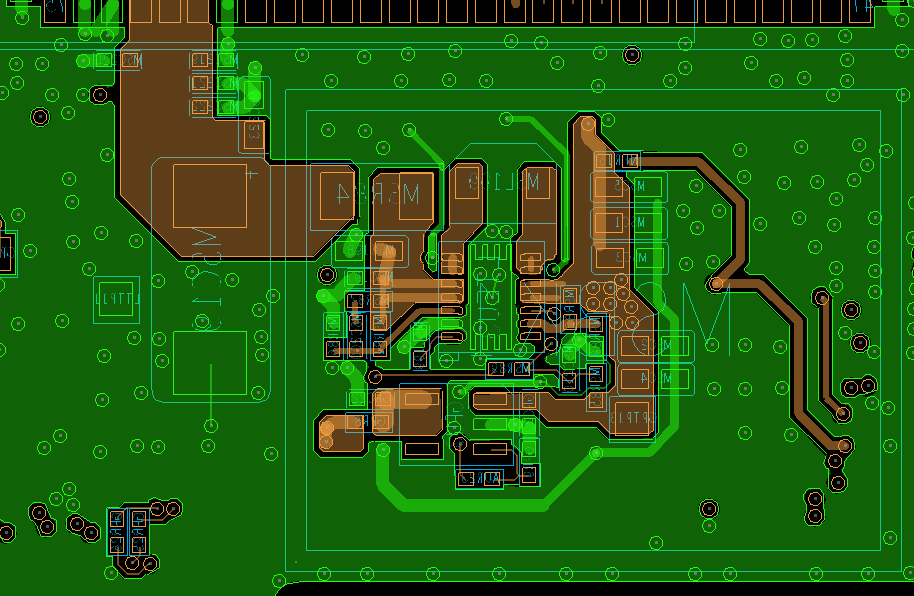

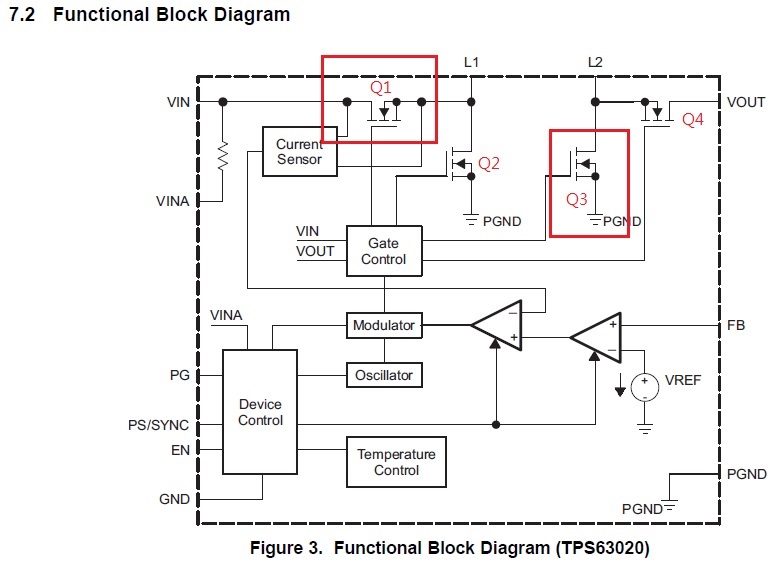

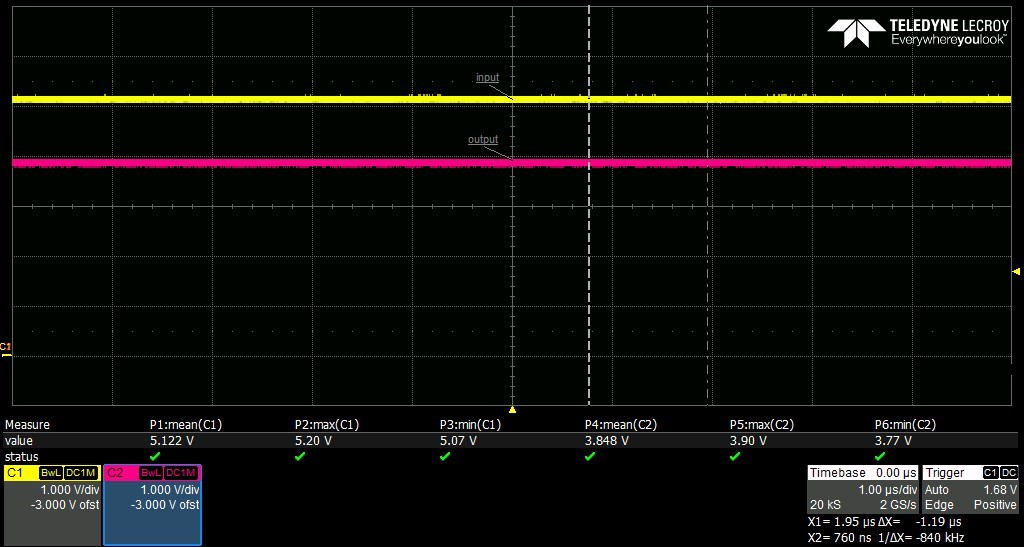

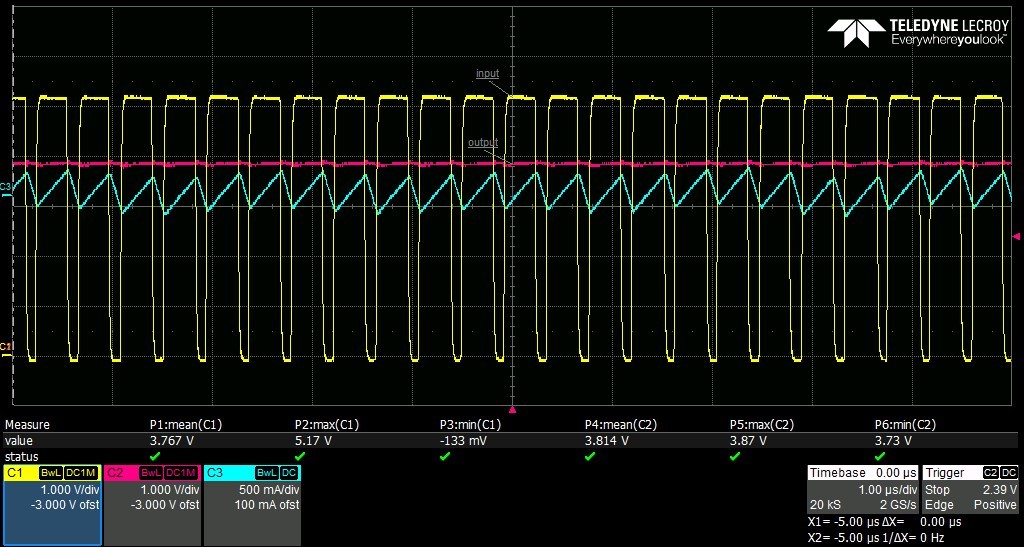

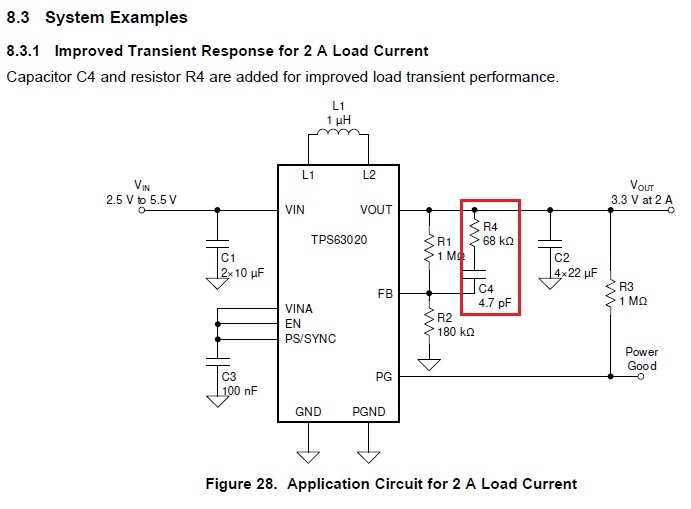

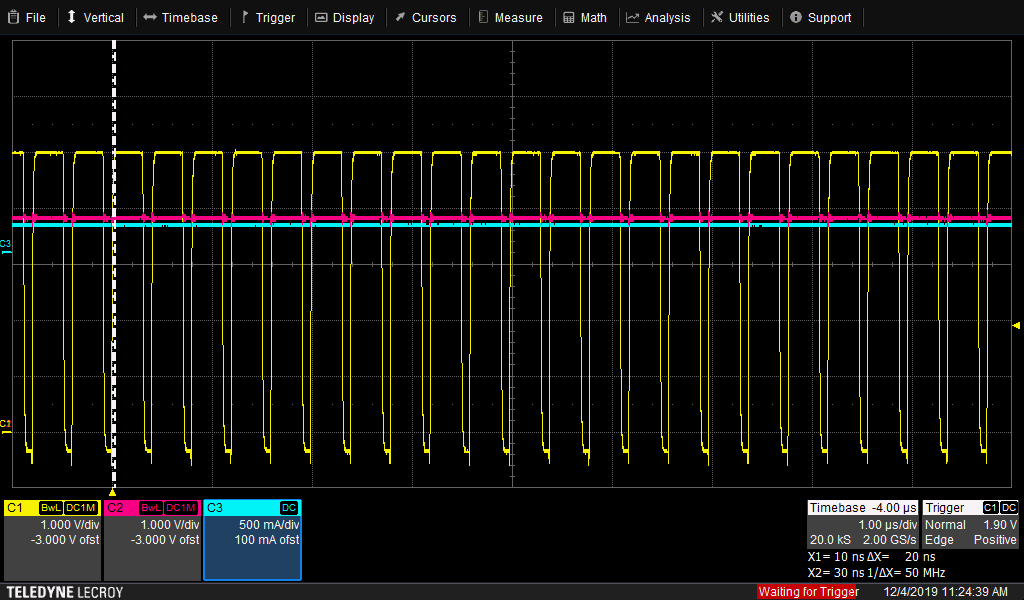

We used TPS63020 to provide LTE power. Input voltage is 5V and output voltage is 3.8V. We disable power saving mode by PS/SYNC pin pull up 100K ohm to Vin.

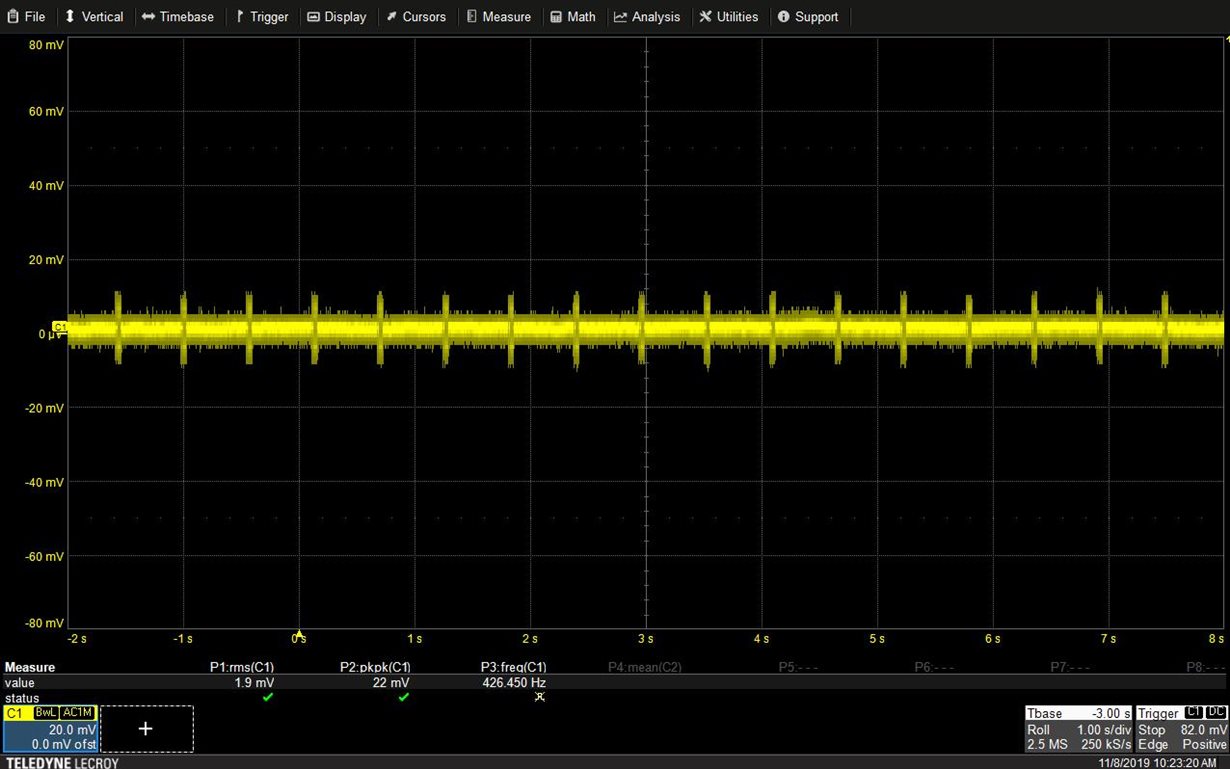

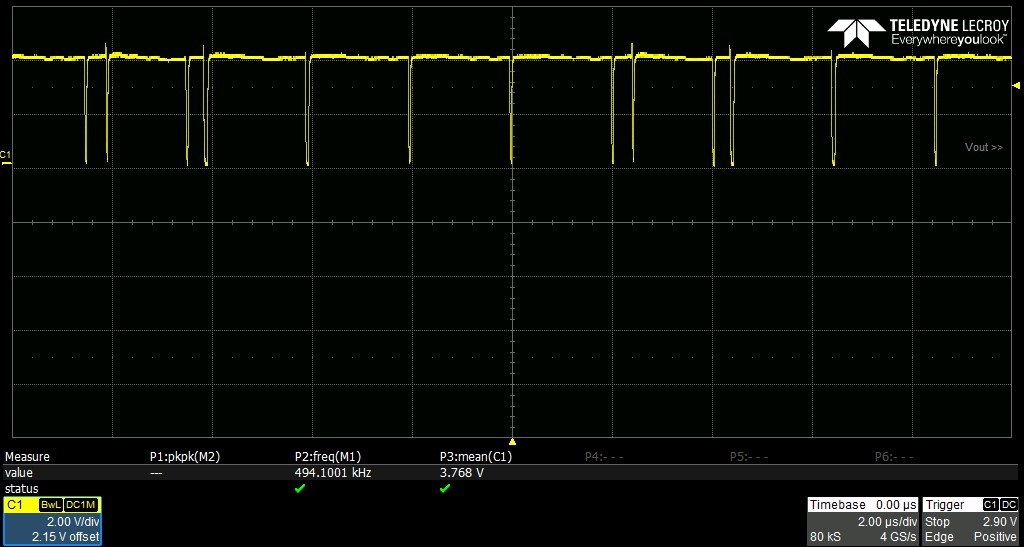

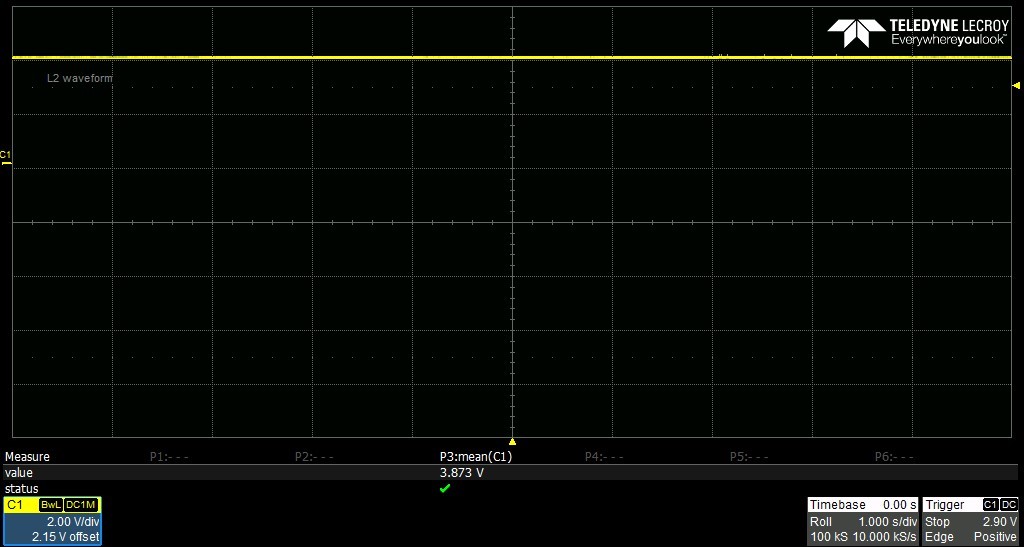

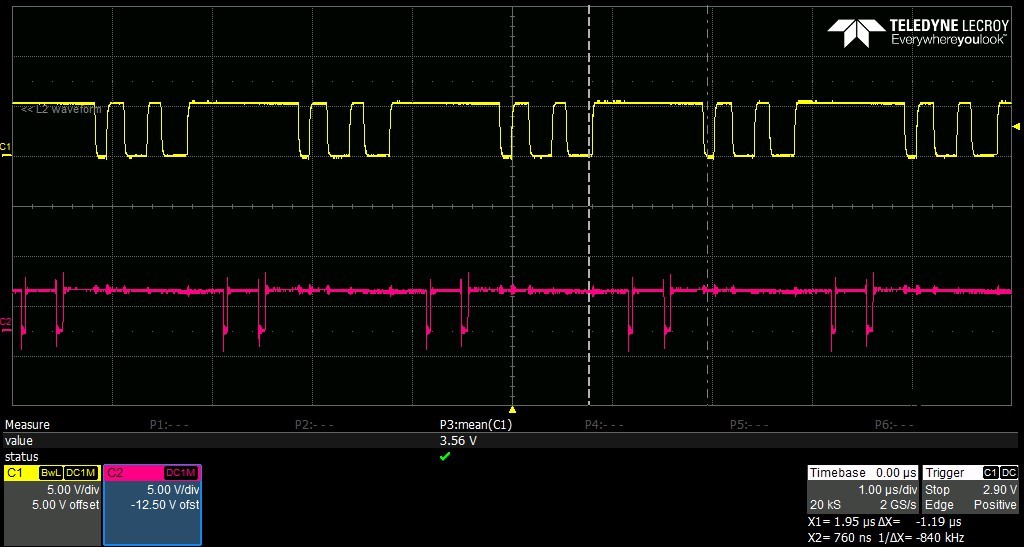

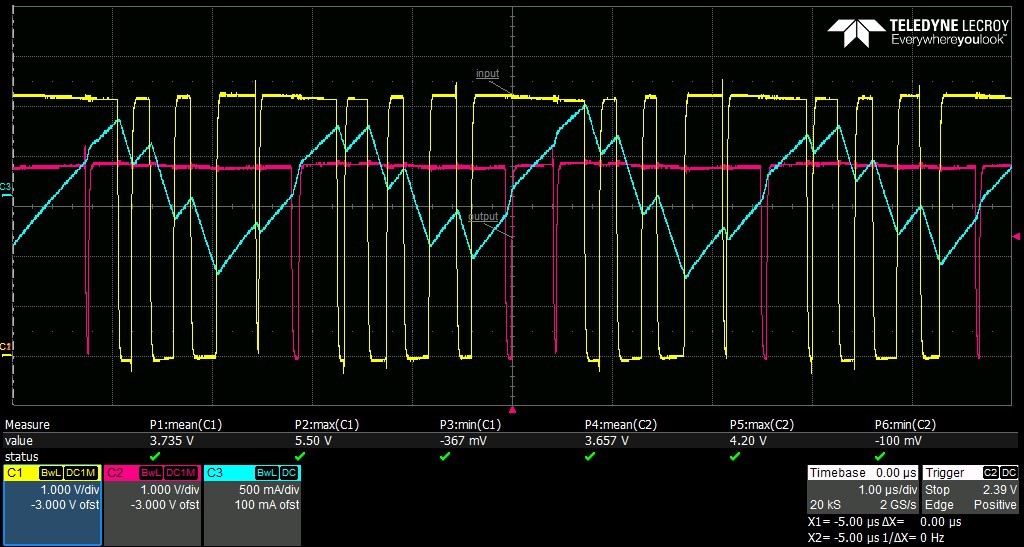

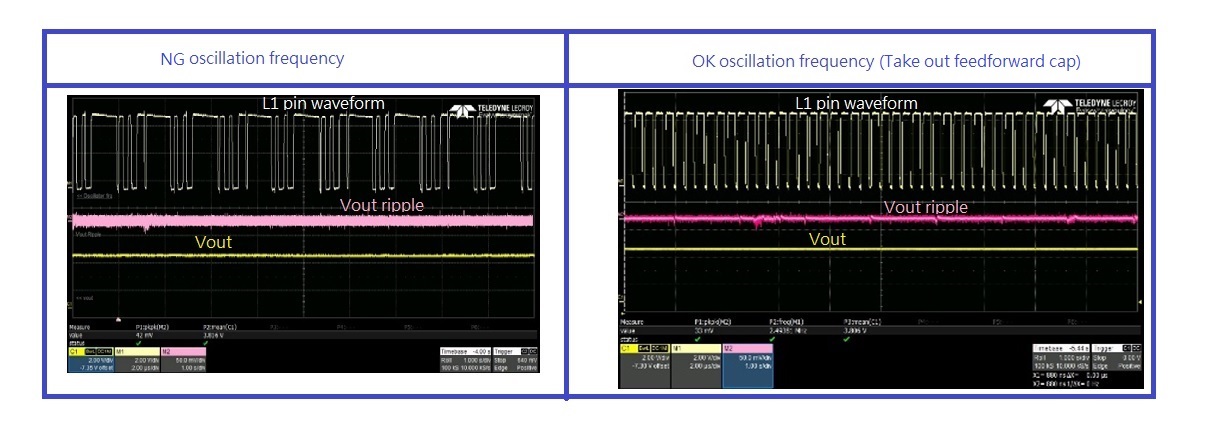

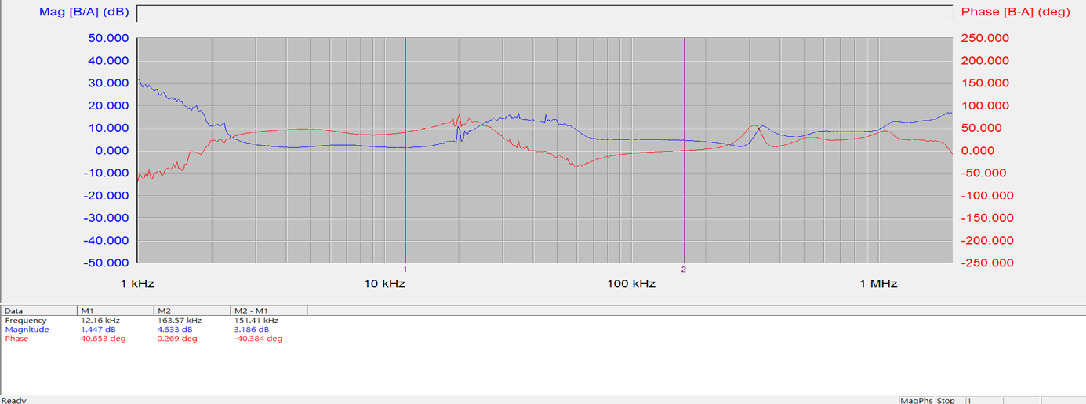

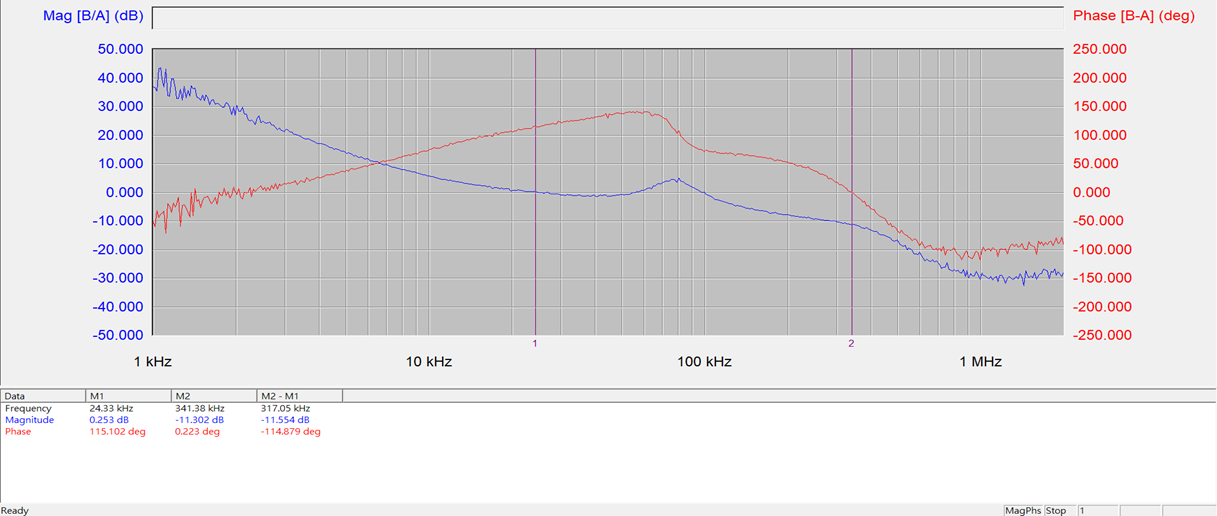

As above, I think oscillator frequecy should be fixed around 2.4MHz and duty may variate by LTE loading. I found one strange symtom that frequency may change to 820KHz sometimes when device runs under -20 degree C temperature. I don't know if it enters power saving mode. Is there any meachanism or cause that TPS63020 possibly operates at this ffrequency? When TPS63020 operates around 820KHz, the output voltage ripple also becomes a little bigger and also FB voltage is around 40mV bigger than normal frequency.

Thank you in advance for the answer.

Sincerely,

Denny