Other Parts Discussed in Thread: SN6505B, UCC23513

Hi,

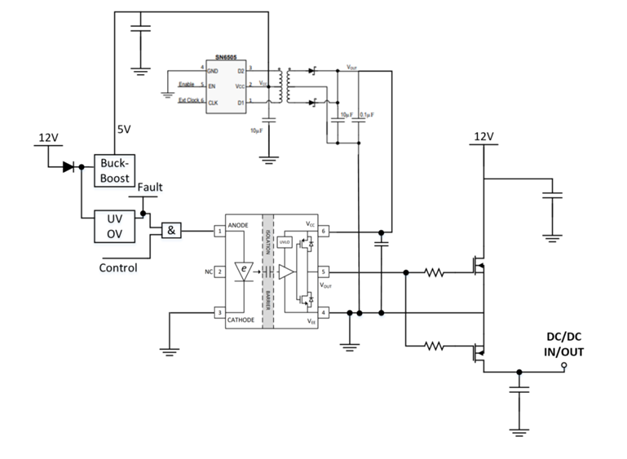

I need UCC21530 to switch 100V through a high side NMOS and low side NMOS to provide Ground as per the attached schematic. The high side NMOS is continuously ON continuously and OFF for a duration of 3ms when needed (actual circuit using a microprocessor based on a logic).

I tried to simulate but I get errors and the OUTA does not switch to OFF. Attached is the circuit. Can you tell me what I am doing wrong?

Thanks,