Other Parts Discussed in Thread: TPS54824

Hi Team,

Here is a question on SS pin of TPS54622.

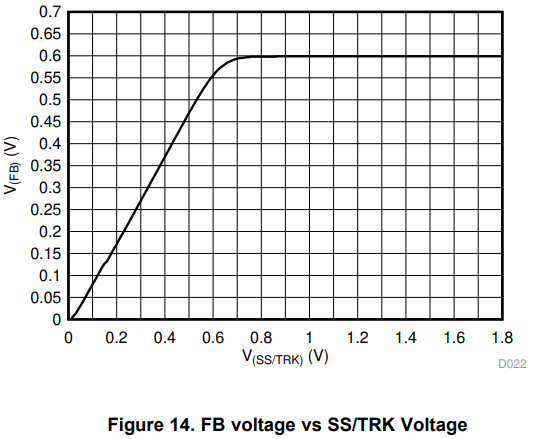

1. in datasheet, it mentioned that in pre-bias startup, low side FET is not allowed to closed until SS voltage goes to 1.4V. So based on my understanding, that is, SS ramp from 0.8V to 1.4V which correspond to Vref from 0V to 0.6V, is it right?

2. is there internal clamp on SS pin and what's the voltage of it?

Thanks.

BRs

Given