Dear Sir,

I have some questions for below.

could you please advise me about below list.

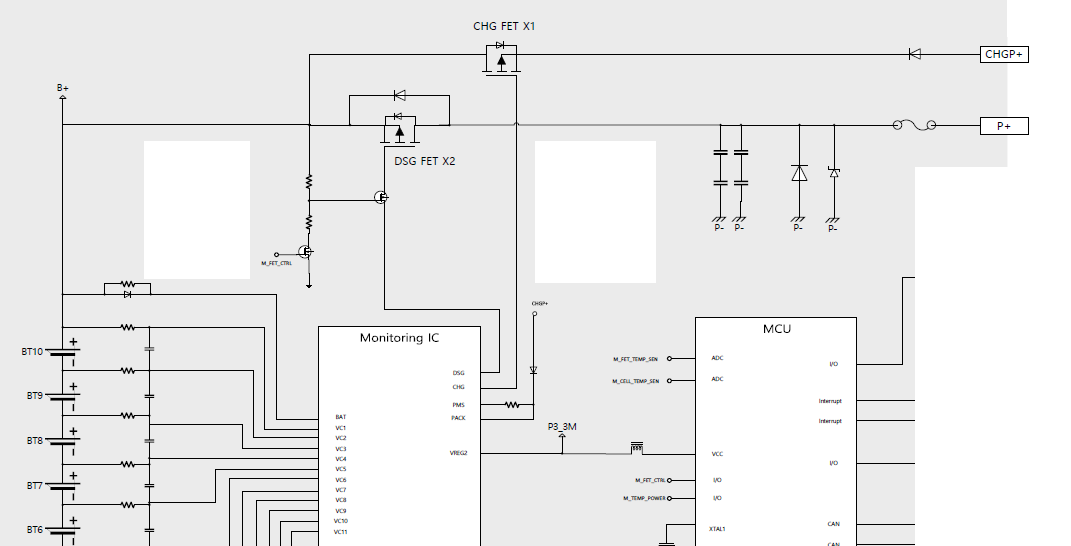

1. If there is a circuit for reference when separating FET of the charging / discharging as like below picture, could you let me know side effect.

2. BQ77PL900 Balancing Related

A. Reason for limiting to Balancing R 500ohm ~ 1kohm.

B. bq77PL900EVM-001 EV kit 510oohm setting reason and balancing current (maximum,minimum) limit.

C. the internal block diagram for Cell sensing & balancing PIN and leakage current of each PIN.