Hi team,

I have a question about the OCP functionality.

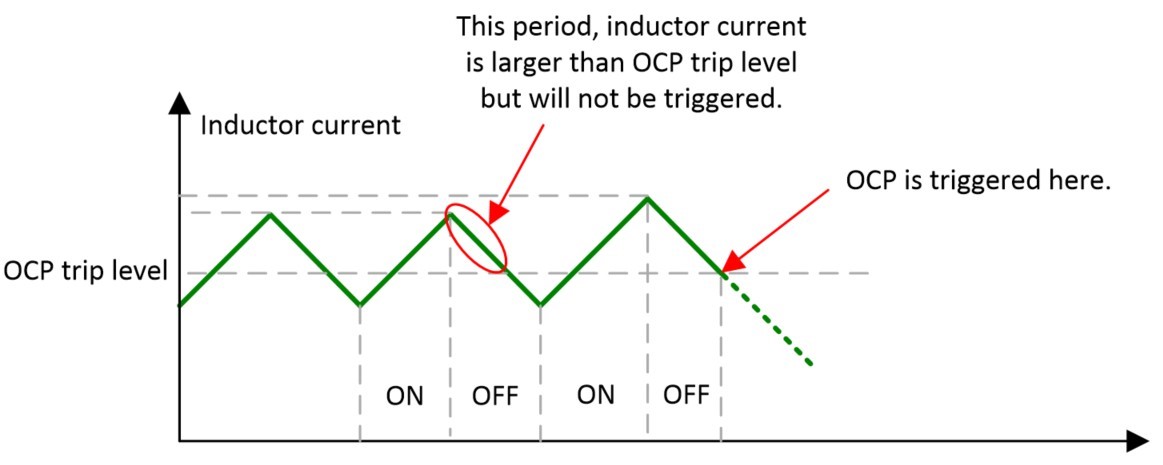

The DS says " TPS53819A has cycle-by-cycle overcurrent limiting control. The inductor current is monitored during the OFF state."

My question is that how the device decides that OCP should be triggered? Or say what's the exact time that the inductor current is monitored?

One idea is that, the device will monitor the inductor current during the whole OFF period, the OCP will be triggered only if inductor current of the whole OFF period is larger than OCP trip level.

Another idea is the device will monitor the inductor current during the whole OFF period, but the OCP will be triggered only needs the vally point of inductor current is larger than OCP trip level.

thanks a lot.

Yang